CMOS数字集成电路是互补金属氧化物半导体数字集成电路的简称,这里C表示互补的意思。它是由P沟道MOS管(以下简称P沟管)和N沟道MOS管(以下简称N沟管)组合而成的。CMOS电路在数字仪表、数字通信、微型计算机、宇宙空间电子系统等方面得到了广泛的应用,这种电路本身具有下述独特优点:

1.微功耗。比普通PMOS电路功耗低1个数量级以上,比双极型电路低几个数量级。

2.电源电压允许变动范围宽。PMOS和双极型电路通常要求电源电压基本恒定,最多不得超过额定值的±10%,而CMOS在3伏~15伏范围内均能正常工作。

3.抗干扰能力强,直流噪声容限典型值可达电源电压的45%左右。

4.速度比PMOS快1个数量级以上。随着工艺方法的不断改进,CMOS的速度还在不断的提高。

5.扇出系数大。

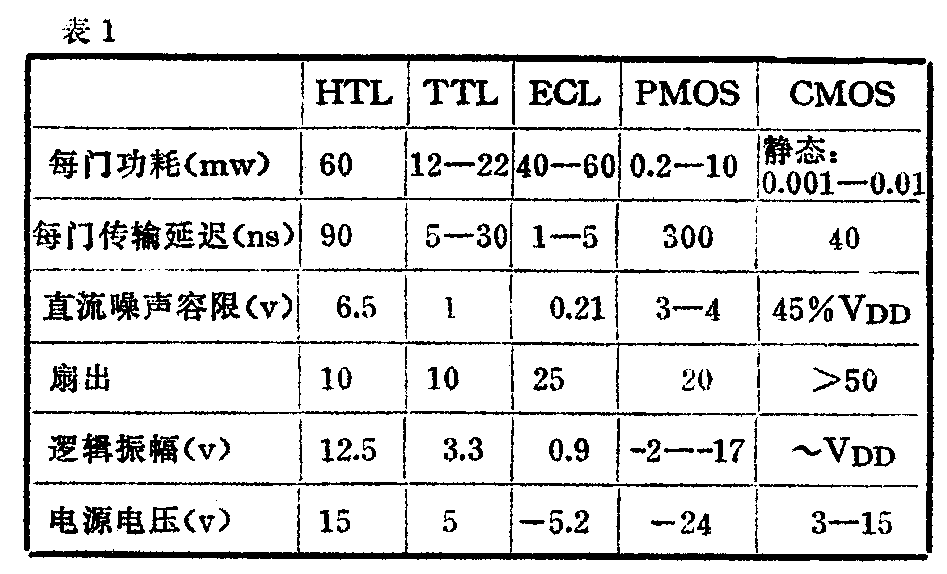

其它主要性能比较见表1。

工作原理

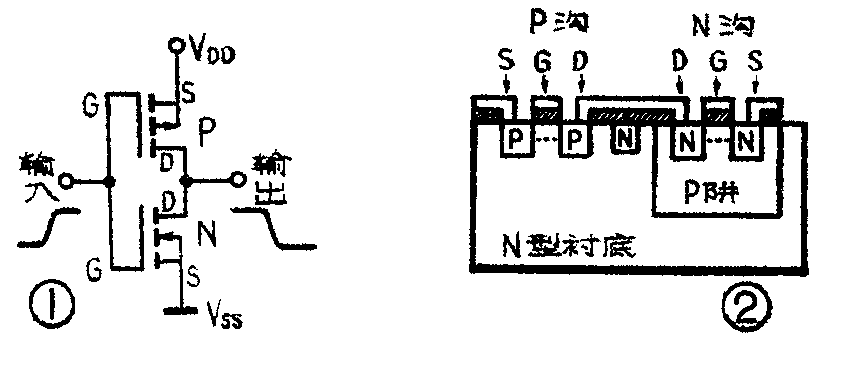

CMOS电路从小规模到中、大规模品种繁多,但这些电路大都是由两个基本电路(反相器和传输门)组成的。图1为CMOS反相器电路图。由图不难看出,它是由P沟管和N沟管组成的,P沟管作负载,N沟管作输出驱动管,P沟管的栅极G与N沟管的栅极G接在一起作输入端,P沟管的漏极D与N沟管的漏极D接在一起作输出端,P沟管的衬底与源极一起接到正电源,N沟管的衬底与源极一起接到地。图2是CMOS的剖面示意图。

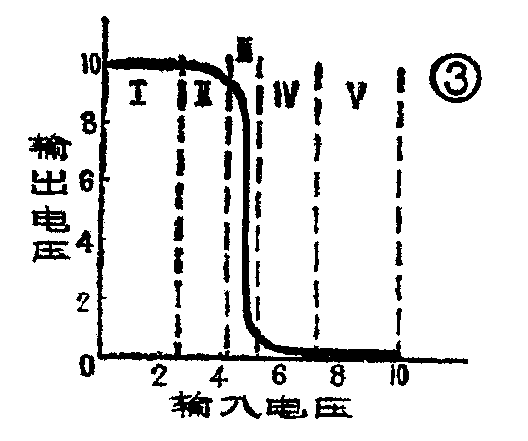

图3为CMOS反相器的电压传输特性曲线,我们结合图1和图3来看看它的工作原理。当输入电压为零时,N沟管的栅极和源极是等电位的,在栅极和衬底之间无电场产生,因此N沟管截止。而此时对P沟管来说,栅极源极之间有较大的负电压,栅极和衬底之间产生电场,形成沟道,因此P沟管导通,这时,输出为高电平。

输入电压由零开始逐步增大,直到大于N沟管开启电压时,N沟管开始导通;P沟管工作在非饱和区,漏源间开始有压降,因此,输出电压开始降低。见图3Ⅱ区。

输入电压继续增大,达到图3中的Ⅲ区时,输入电压的少量增长,都会引起输出电压的急剧下降,此时P沟管和N沟管均工作在饱和区,流过较大的电流,引起输出电压由高到低的跳变,形成动态区。

输入电压继续增大而进入到Ⅳ区时,P沟管工作在饱和区,降压大;N沟管工作在非饱和区,降压小,输出电压随之逐步降低。

当输入电压进入到Ⅴ区时,P沟管的栅源电压小于其开启电压,这时P沟管完全截止,N沟管继续工作在非饱和区,输出为低电平。

简单说来:当输入为低电平时,N沟管截止,P沟管导通,反相器输出为高电平;当输入为高电平时,N沟管导通,P沟管截止,反相器输出为低电平。

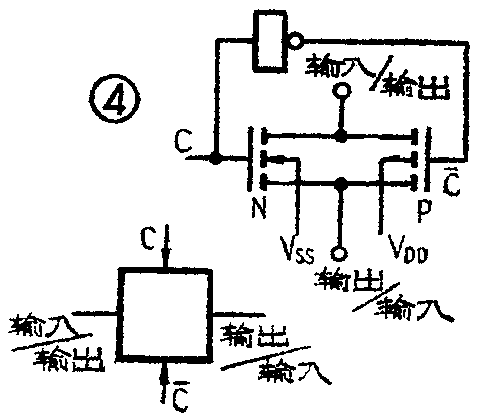

图4是CMOS传输门电路图和符号。它是由P沟管和N沟管并联而成的,P沟管的源极S和N沟管的漏极D连接,作为输入端(或者输出端);P沟管的漏极和N沟管的源极连接,作为输出端(或者输入端);P沟管的衬底接到V\(_{DD}\);N沟管的衬底接到VSS;P沟管的栅极和N沟管的栅极分别接到一对互为反相的控制信号C和C-端。当控制信号C为高电平,C-则为低电平,这时,对N沟管来说,栅极对衬底是正电压,对P沟管来说,栅极对衬底是负电压,都形成沟道,因此P沟管和N沟管都导通,导通电阻约几百欧姆,输入信号可传输到输出端。当控制信号C为低电平,C-则为高电平,这时,N沟管的栅极和衬底为等电位,P沟管的栅极和衬底亦为等电位,所以P沟管和N沟管都截止,截止电阻可达几十兆欧到几百兆欧,输入信号不能传输到输出端。

由于MOS管结构对称,源极和漏极可以互换,电流可以由两个方向流通,即可由输入端流向输出端,亦可由输出端流到输入端,具有双向特性,所以传输门又叫做双向开关。功能上相当于单刀单掷开关。

由于CMOS传输门输入输出电压线性度较好,所以可以单独用作双向模拟开关构成一个产品,广泛用于模—数、数—模变换器中。

传输门和门电路组合起来又可构成CMOS触发器、计数器、移位寄存器、运算单元和存贮器单元。

CMOS基本数字电路

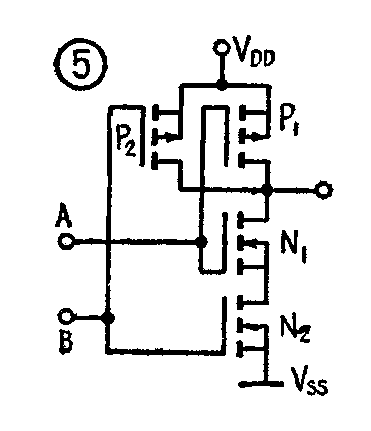

1.与非门。图5为二输入端CMOS与非门电路图。它是由两个P沟管并联、两个N沟管串联组合而成的。当输入端A和B都为高电平时,两个N沟管都导通,两个P沟管都截止,输出为低电平;当输入端A和B都为低电平时,则两个N沟管都截止,两个P沟管都导通,输出为高电平;若输入端A为高电平,B为低电平,则N\(_{1}\)导通、N2截止、P\(_{1}\)截止、P2导通(或者相反),输出为高电平。

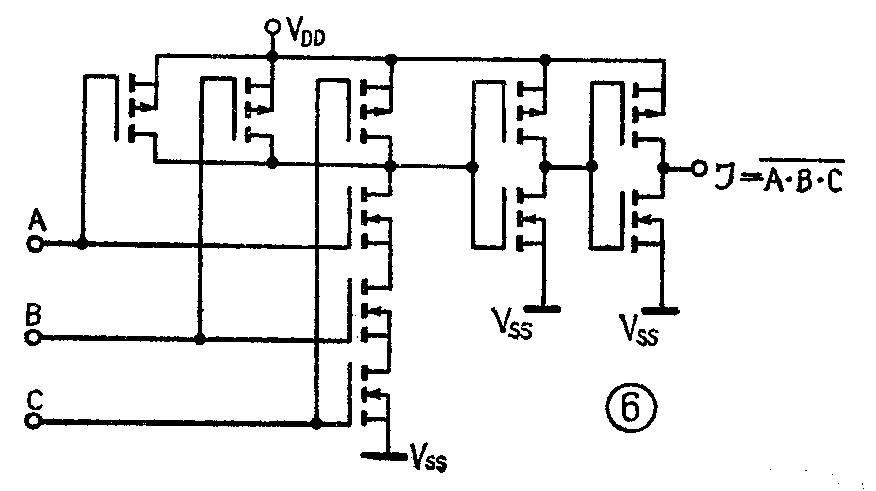

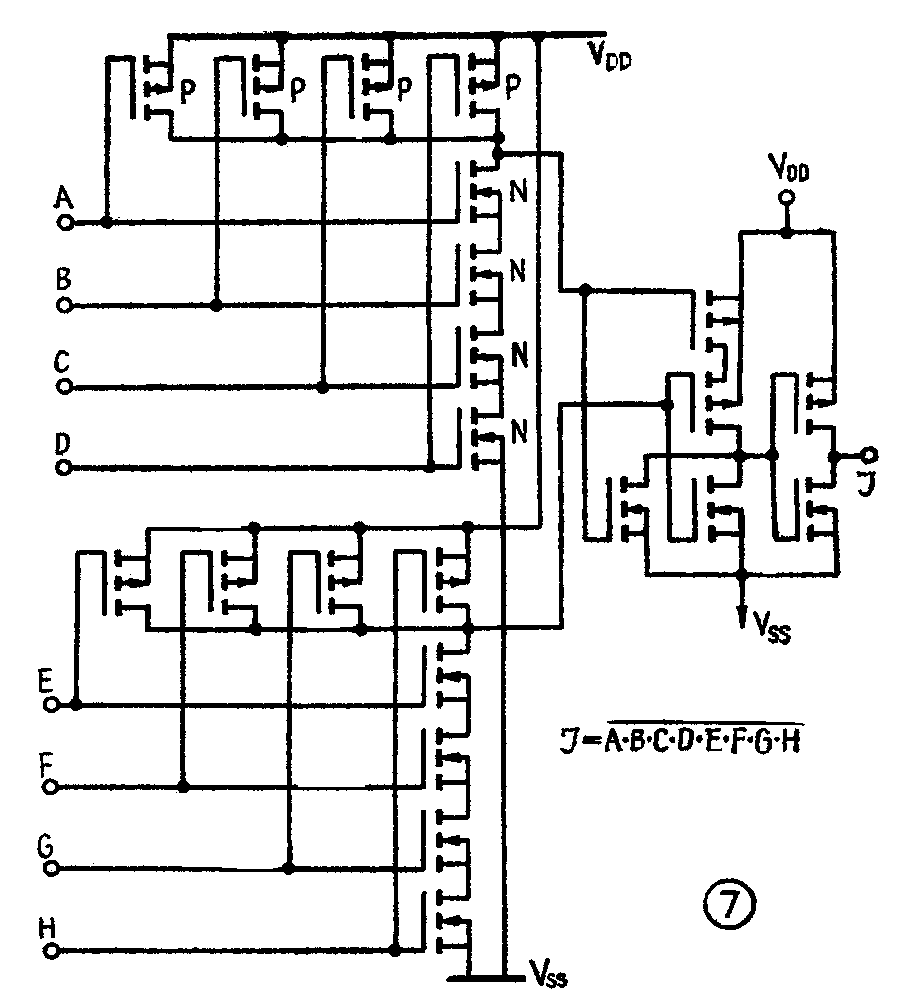

对于三输入端、四输入端与非门,则需相应增加N沟管和P沟管数。图6为三输入端与非门电路图。输入端数受N沟管串联数目的限制,为了保证电路的直流噪声容限,计算和实验都表明,输入端数最多为4个。如果需要输入端数大于4的与非门,可以采用电路组合的办法来扩展,图7为8输入端与非门电路图。

为了改善电路性能,有不少的门电路产品,是在基本门电路上再加上两个反相器,如图6所示。

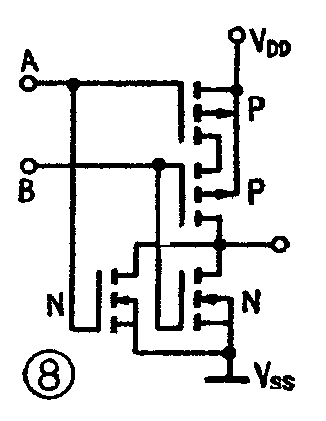

2.或非门。图8为二输入端或非门电路。和图5的与非门电路比较一下,不难看出,或非门正好和与非门相反,它是P沟管串联、N沟管并联而成的。同样,或非门的输入端数也限定为4个,多于4个输入端的或非门也是采用电路组合而成的。和与非门一样,也有不少产品是在基本或非门的基础上再增加二级反相器来改善电路性能的。

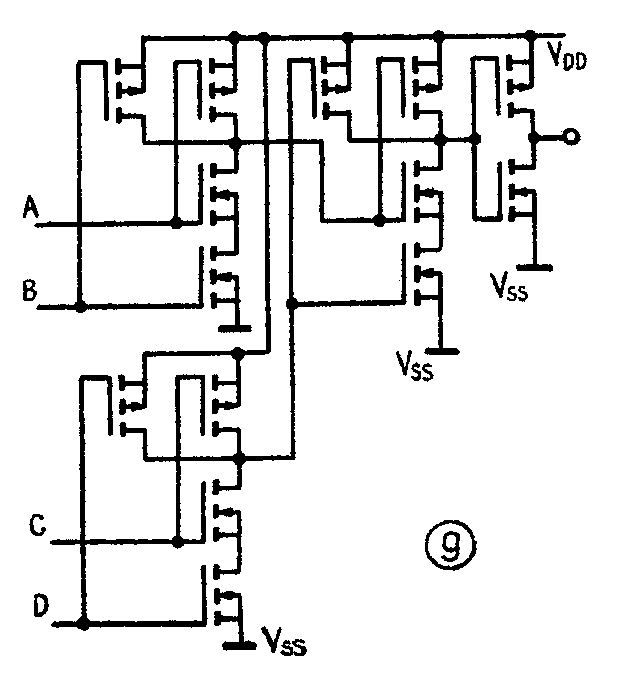

3.与或非门。图9为CMOS与或非电路图。由图可见,它是由与非门加反相器组成的。

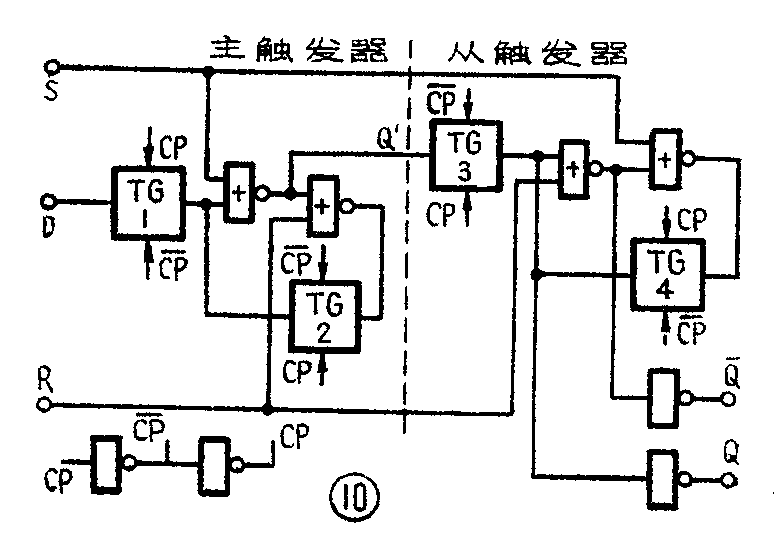

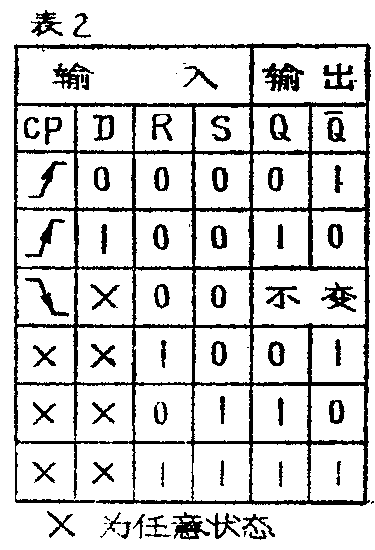

4.D触发器。CMOS触发器和TTL触发器结构上有所不同,主要差别是在信号导引电路上,CMOS是依靠传输门来导引信号的。图10为CMOS D触发器逻辑图。由图可见,它是由两个R-S触发器级联而成的主从触发器。传输门TG\(_{2}\)和两个或非门组成主触发器,传输门TG4和两个或非门组成从触发器。当CP=0时,传输门TG\(_{1}\)、TG4导通,TG\(_{2}\)、TG3截止,这表明主触发器的输出Q′是D输入端的反码,而从触发器状态不变,保持记忆。当CP跳变到1时,则传输门转换为下列状态:TG\(_{2}\)、TG3导通,TG\(_{1}\)、TG4截止,主触发器由于TG\(_{2}\)导通保持记忆,并由TG3直接把信号送到从触发器的输出端Q。所以,D输入端的数据是在时钟脉冲CP的上升沿传送的。与TTL触发器不同,CMOS D触发器的非同步输入端R、S,是在输入高电平时起置数、置 零作用的,R、S端不使 用时,应始终处于低电平。R、S的功能与CP的状态无关。其真值表如表2。(应兵)