集成电路触发器的种类很多,线路也比较复杂,但它们都是由一些最基本的逻辑门按照一定的方式组合起来的。为了进一步了解各种实际触发器电路,首先要掌握集成电路逻辑门以及组成这些门的最基本单元—半导体开关的原理。在这里,我们结合实际触发器电路,介绍晶体管—晶体管逻辑(TTL)、金属—氧化物—半导体(MOS)和互补MOS(CMOS)三种应用比较广泛的逻辑门及相应的半导体开关。为了掌握这些器件和电路的原理,把它们转换为简化开关模型及由开关组成的模型电路来分析,是一种直观而又简便的方法。

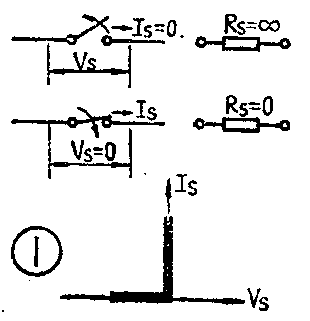

理想开关

开关这个概念早已为大家所熟悉。图1是一个理想开关的电路图及其特性。当它处于断开状态时,它两端的电阻R\(_{s}\)=∞,外部电压Vs全部降在开关的两端;而当处于合上状态时,开关电阻R\(_{s}\)=0。由于不论处于何种状态,这种开关消耗的功率为Vs·I\(_{s}\)=0,所以理想开关本身不消耗功率却能操纵大功率信号。理想开关往往被当作一种分析实际半导体开关的简化模型,实际上并不存在真正的理想开关,它只是设计各种实际开关所力图接近的目标。

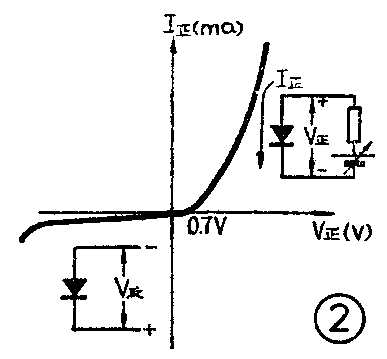

二极管和三极管开关

图2是一个典型硅二极管的伏安特性,当二极管两端加正向偏置电压V\(_{正}\)时,起初通过它的正向电流I正很小,大约过了0.7V后,曲线迅速向上拐去,形成一个很小而又接近恒定数值的动态电阻R\(_{s}\)=△V正/△I\(_{正}\),这时相当于开关的合上状态。反之,当二极管两端加反向偏置电压V反时,反向漏电流I\(_{反}\)很小,二极管表现出一个很大的电阻,相当于开关的断开状态。由此可见,只要适当选择外部电路条件,就可以把二极管作成一个开关。与理想开关相比较,它在正向电压作用下(合状态)具有一个很小数值的电阻,而在反向电压的作用下(断状态)其阻值不是无穷大。另外,在正向电压作用下有一个0.7V的“死区”,相当于反向串接一个电源,越过了它,二极管才真正相当于合上的开关。

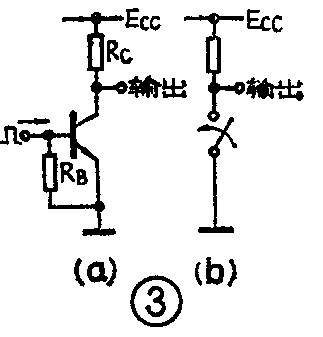

在集成电路逻辑门中,更多地是采用晶体三极管开关。图3a是一个最简单的饱和开关电路,图3b是其模型电路。当晶体管的基极输入电压为零或负值时,I\(_{b}\)=0,晶体管处于截止状态,它的集电极—发射极间阻抗很大,相当于一个断开的开关;当输入电压为正,并向基极注入足够大的正向电流时,晶体管进入饱和状态,集电极—发射极间的阻抗很小,其间的压降接近于零,相当于开关的合上状态。

在晶体管开关中,输入控制信号不象二极管开关那样直接通过开关本身,而是加到基极,然后在集电极回路中产生一个相应的输出信号。一般说来,其输入控制信号在微安和毫伏级,而输出信号在毫安和伏特数量级,也就是说它具有放大作用,这也是晶体管开关的优点之一。

晶体管—晶体管逻辑(TTL)与非门

TTL集成电路是目前应用最广泛的品种之一,这种集成电路的基本开关元件是晶体管,逻辑门的基本形式是与非门。

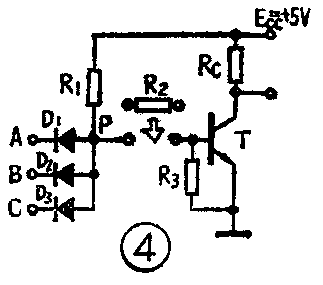

为了理解TTL与非门的原理,先来看一个最简单的二极管与门和一个饱和式晶体管反相器(非门)所组成的与非门(图4)。假定图中电路的三个输入端中的一个处于低电平(A=0),则二极管D\(_{1}\)导通,有电流Ird流过,称为输入短路电流。因为此时P点的电位接近于零,所以晶体管T截止,输出端呈现高电平、实现了与非逻辑功能。实际上由于二极管有正向压降(硅二极管约为0.7V),所以D\(_{1}\)导通时P点电位不是0V而是0.7V。这样,只要与非门的输入端有一个很小的干扰电压出现,它都能叠加在0.7V上使晶体管T很容易地由截止状态转入饱和状态,破坏固有的正确逻辑关系。因此在这种情况下有必要在两个门的交界处设置一个足够大的电阻R2,使晶体管T的基极电位低于P点电位。从而对出现在输入端的干扰信号不那么敏感。

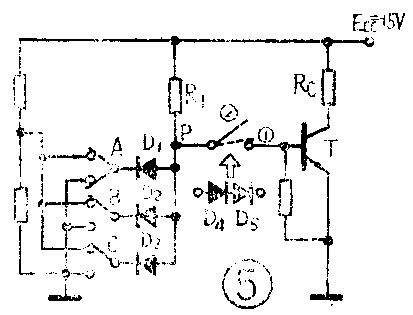

再来看三个输入端都处于高电平,即A=B=C=1的情况。此时三只二极管D\(_{1}\)、D2、D\(_{3}\)在高电平输入信号的作用下处于反向偏置(二极管开关断开),因此P点呈现高电平,使T进入饱和状态,该晶体管的集电极出现低电平,实现了与非逻辑功能。为了使晶体管进入深度饱和,必须向它的基极提供足够大的注入电流,很明显,这时就希望电阻R2愈小愈好,否则无法提高注入电流。由此可知,在两种输入信号情况下,对R\(_{2}\)的要求刚好相反,因此想到,最好用一个开关来代替R2,如图5所示,当所有输入信号都为1时,这个开关合上(位置①),电阻R\(_{2}\)很小,输出晶体管很容易饱和;而当有0输入信号时开关断开(位置②),使晶体管较稳定地处于截止状态。这样自动启闭的开关,可以用二极管D4、D\(_{5}\)来近似地实现,在电路中,由于它们能使晶体管基极的电位相对于P点的电位产生一个偏移,因此被称为电平位移二极管。

电平位移作用是通过利用二极管的开关特性来获得的。如图5所示。当P点处于高电平(A=B=C=1)时,二极管D\(_{4}\)、D5受正偏,因此导通。而当P点处于低电平(例如A=0,B=C=1)时,使晶体管T导通的P点从电位V\(_{p}\)至少应满足Vp≥V\(_{D4}\)+VD5+V\(_{be}\)=2.1V,在Vp<2.1V的情况下,因为二极管开关D\(_{4}\)、D5总处于断开状态,所以晶体管T也只能处于截止状态。因此在P点出现的低于2.1V的干扰信号都不会产生影响,这就提高了电路的抗干扰能力。

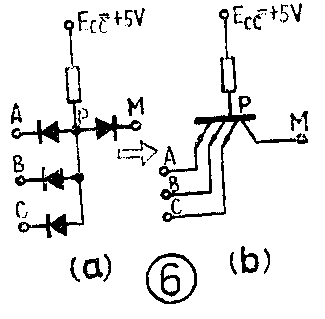

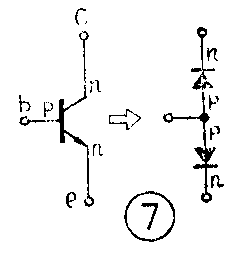

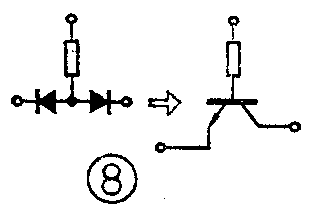

为了说明TTL电路是怎样演变出来的,将图5电路左半面的二极管与门和电平位移二极管单独画出来(图6a),因为晶体管刚好相当于两只背靠背接在一起的二极管(图7),所以可用晶体管的两个反向结来代替这两个背靠背的二极管(图8)。

实际的电路不仅采用了晶体管,而且将它做成多发射极的形式(图6b)。这样,不仅从工艺和结构上进行了简化,而且还改善了电路的性能。多发射极晶体管的原理与一般单发射极的没有什么区别,只是增加了输入端的个数。

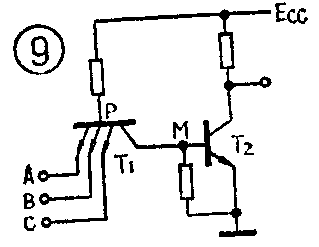

图9画出了最简单的TTL与非门。当所有的输入端都处于高电平时(例如A=B=C=3.3V),发射结二极管处于反偏,P点电位约为1.4伏,集电结二极管导通,M点也处于高电平(M点电位与P点的相差0.7V,本例中约为0.7V),使晶体管T\(_{2}\)处于饱和状态,输出低电平(逻辑0)。当任一输入端处于低电平(例如VA=0V)时,则晶体管T\(_{1}\)的两个结都处于正向偏置状态,T1进入饱和状态,T\(_{2}\)截止,输出高电平(逻辑1)。

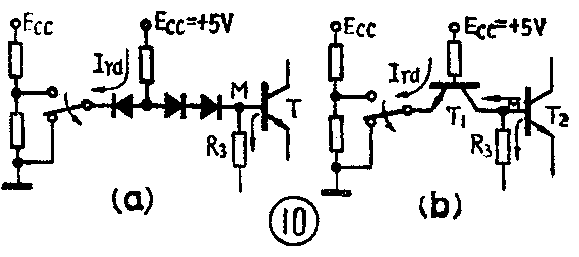

当输入信号由1→0时,在图10a的电路中因为有电平位移二极管存在,所以输出晶体管的基区存贮电荷只能沿R\(_{3}\)泄放出去,从而相对地拉长了晶体管转入截止的过程。TTL电路(图10b)则不这样,当输入信号由1→0时,输入晶体管的射极电位突变到0,但M点的电位还未马上降下来,所以有一个放大了的集电极电流通过晶体管T1的集电极和发射极流回到地。这样,就为晶体管T\(_{2}\)提供了一个反向基极电流,可以很快地抽出多余的基区存贮电荷,使门的动作时间大大缩短。

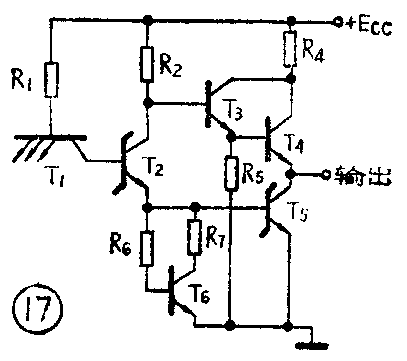

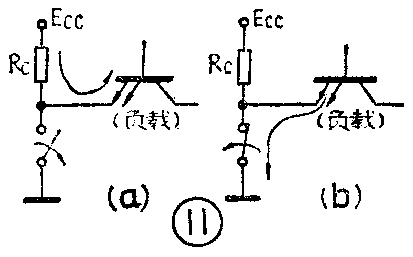

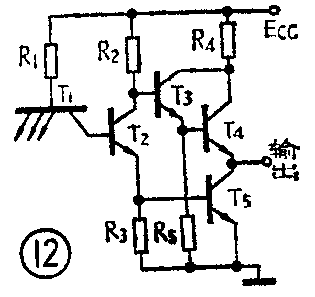

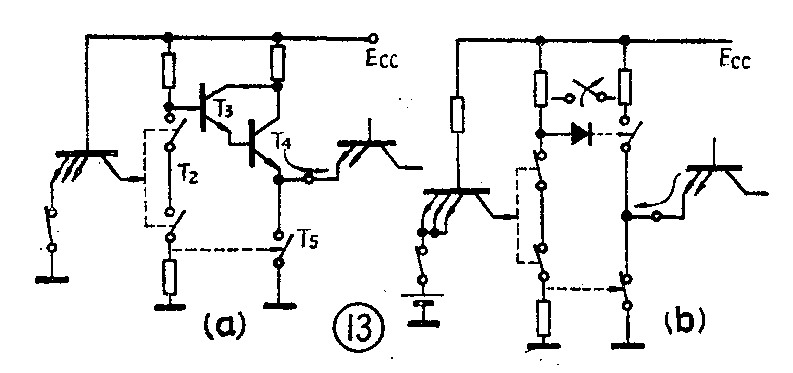

以上着重介绍了TTL门的输入级,下面再来看输出级。为了便于分析起见,将图9中右半部分输出级的模型电路取出来分两种情况画成图11。第一种情况下(图11a)反相器晶体管(一般叫做输出门控管)截止,输出高电平,我们用一个打开的开关来表示。此时,为了减少输出漏电流在R\(_{c}\)上产生的压降对下级负载的影响,希望Rc越小越好。与此相反,若输出门控管饱和(开关合上),则为了更好地隔离电源与逻辑门的输出端并尽量减少流过R\(_{c}\)的电流起见,又希望Rc越大越好。可见,用一个简单的电阻作门控管负载是不能满足要求的。图12示出了一种典型的TTL中速与非门电路。在该电路中将原来的输出反相级扩充为具有两个相位相反的输出信号的放大级,同时对两个对象进行控制:一个是输出门控管T\(_{5}\),另一个是动态负载T3、T\(_{4}\)。图13是用开关表示各晶体管动作的模型电路:当输入端有一个为0(接地)时(图13a),晶体管T2截止,门控管T\(_{5}\)截止,输出逻辑1。此时接成复合管的T3、T\(_{4}\)导通。构成低输出阻抗射极输出级,提高了驱动负载的能力;当输入全为1时,晶体管T2饱和(图13b),使门控管T\(_{5}\)饱和,输出逻辑0,同时,T3、T\(_{4}\)在很低的基极电位的作用下转入截止,T3的发射结相当于一个电平位移二极管,操纵半导体开关T\(_{4}\)断开,使门控管T5的等效集电极电阻很大,所以能够满足上述对门控管负载所提出的要求。

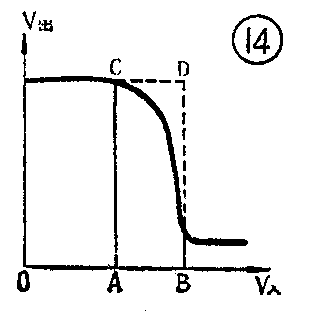

在上述TTL中速与非门中,当输入电压从低电平增加到高电平时输出电压随之变化的关系曲线称为转换特性(图14)。图中用虚线绘出了理想的转换特性,理想与非门电路的输入信号从0增加达到某一阈值时,应使输出电压立即产生雪崩式的跳变,而实际电路的输出电压从高电平变到低电平要经过一段时间才能实现。这是因为在图12的电路中,随着输入电压的增加,晶体管T\(_{2}\)和T5不能立即同时进入饱和状态造成的,它们都要先从截止状态进入晶体管特性的有源区,工作于放大状态,然后才能进入饱和状态,这样就使门电路的切换速度有所下降。

对于相反的情况即当输入电压从高电平减小到0时,也有切换速度下降的现象发生。这是因为在高电平输入信号的作用下,晶体管T\(_{2}\)、T5处于饱和状态,它们的发射结和集电结均处于正偏,并且集电结所受的正向偏置电压越大,管子就饱和得越深,而管子饱和越深则由饱和状态翻转到截止状态所需要的时间就越长,降低了切换速度。

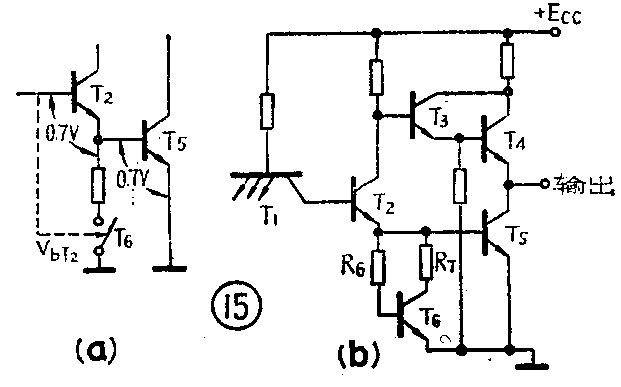

针对上面提到的两种情况,自然会想到:在提高速度方面是否还有潜力可挖呢?对于上面提到的第一种情况,为了尽量缩短晶体管T\(_{2}\)、T5在有源区停留的时间。在T\(_{2}\)的射极接入一个自动开关,如图15,这个开关是由晶体管T6来实现的。在这种电路中,只要T\(_{2}\)的基极电位Vbt2低于1.4V,T\(_{5}\)这个晶体管开关就能保持断开状态,从而使T2处于截止状态,不会进入有源区。直到V\(_{bt2}\)达到或超过1.4V后,T6才能导通,从而使T\(_{2}\)、T5同时进入饱和,得到更接近于理想门电路的较为陡峭的转换特性,提高了切换速度。

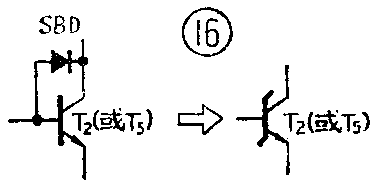

至于第二种情况,即当输入电压从高电平减到0时,为了提高电路的切换速度,应使管子工作于轻度饱和状态。这可以在管子的基—集极间并接一个箝位二极管(图16)来实现。只要这个二极管的正向导通阈电压低于硅PN结的阈电压(0.7V),它就能起箝位作用而抑制T\(_{2}\)或T5的饱和深度。另外,为了加快电路的翻转速度,还要求此二极管的载流子贮存效应尽量小。能够满足这两项要求的二极管是用金属—半导体接触构成的特殊二级管,称为肖特基势垒二极管;(简写为SBD),它的正向导通阈电压只有0.4~0.5V,而且由于导电机构与一般的PN结不同,它是完全没有载流子贮存效应的。加有SBD箝位的晶体管通常用图16的符号来表示。于是我们得到图17所示的电路,这是目前广泛使用的一种高速TTL电路,它的传输延时已可以小到1毫微秒。(颜超)