D触发器(例如SC3102型)是利用时钟脉冲的正跳变触发并且有维持阻塞功能的一种触发电路。用它可以方便地组成二进计数器和十进计数器。

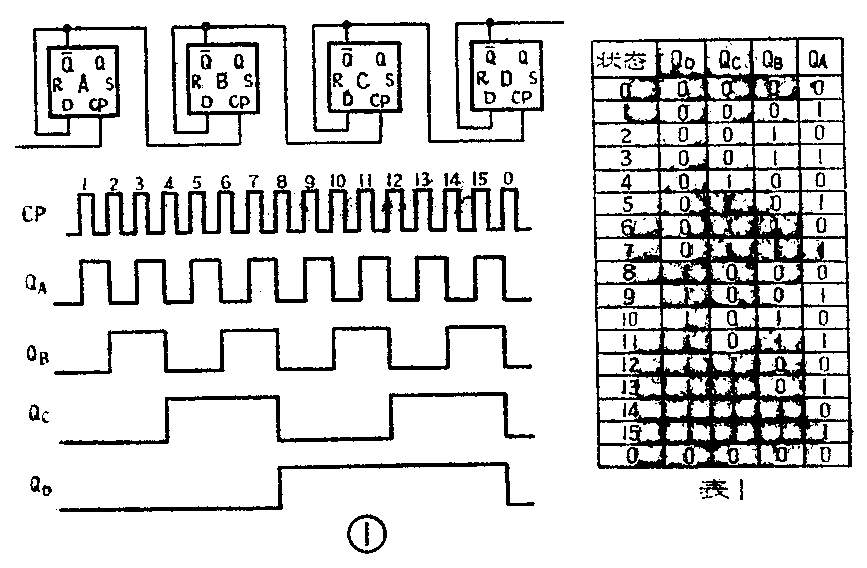

1.串行加法型二进计数器

图1是一种4位二进串行加法型计数器和各级波形图。一个N位二进计数器,每当输入2\(^{N}\)个时钟脉冲,其计数状态就重复一次,例如4位二进计数器就按基数为16的数制顺序计数,并有十六个不同状态,见表1。

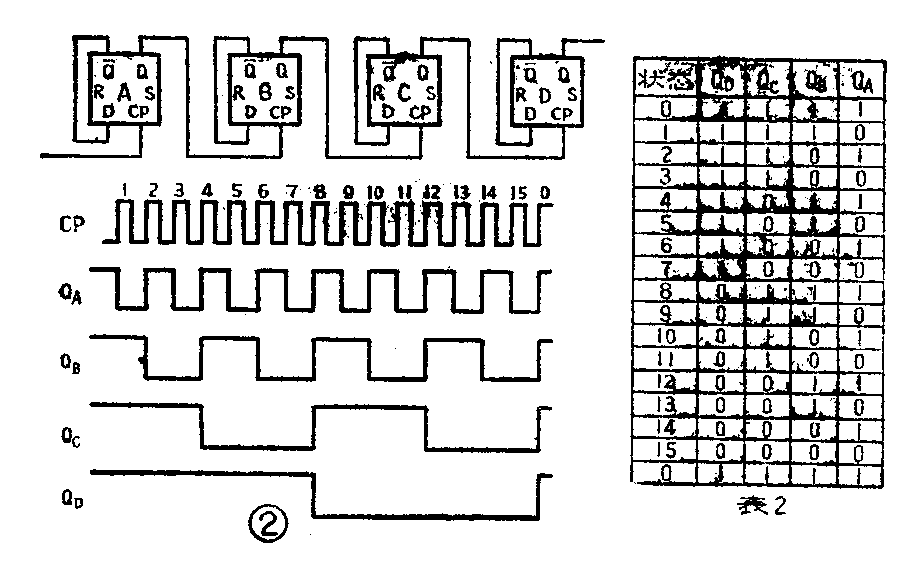

2.串行减法型二进计数器

见图2和表2,与加法型计数器不同之处仅在于将Q\(_{A}\)、QB、Q\(_{C}\)的输出分别作为触发器B、C、D的时钟脉冲输入。

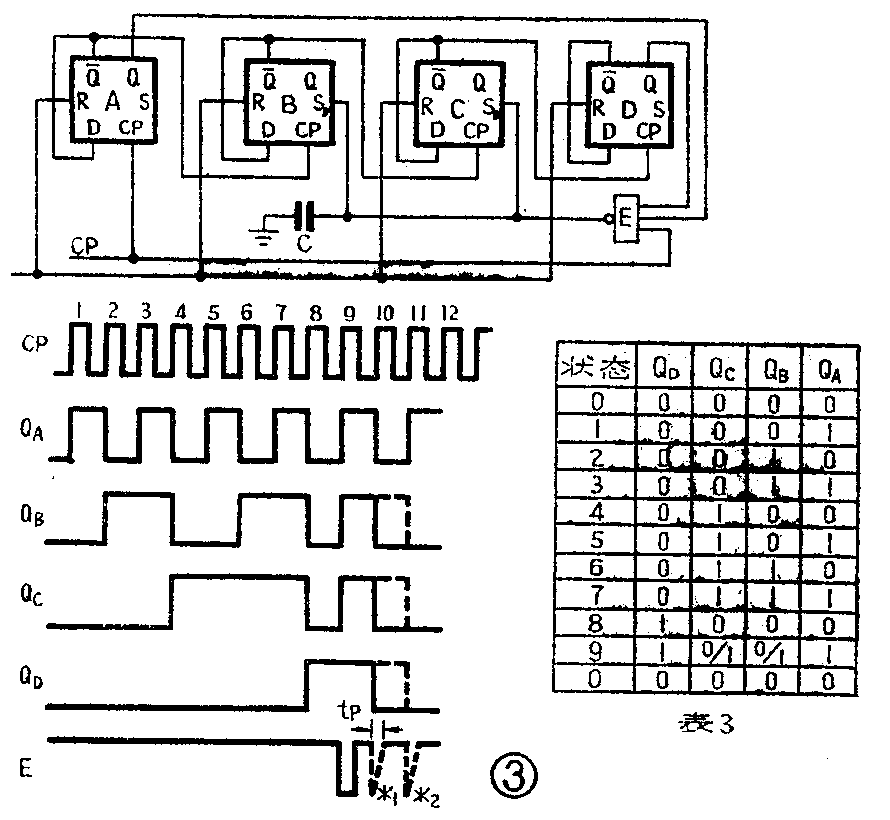

3. 串行十进计数器

将二进计数器接成权为8·4·2·1码十进计数器,可按下列步骤考虑:

(1)求出所需触发器的个数n,2\(^{n-1}\)≤N≤2n,N为计数循环长度,十进计数器N=10,因此n=4。

(2)将4个触发器接成一个串行二进计数器。

(3)查出N—1时的二进制数。

(4)把计数到N-1时Q为“1”的所有触发器的输出端和时钟脉冲分别接到一个与非门的输入端。

(5)与非门的输出端馈送到在计数到N-1时,Q=0的所有触发器的置位端S\(_{D}\)上。

加法型十进计数器N-1=1001,将触发器A、D的Q端和时钟脉冲分别接在与非门E的三个输入端上,将E的输出端接到触发器B、C的S\(_{D}\)端,见图3。

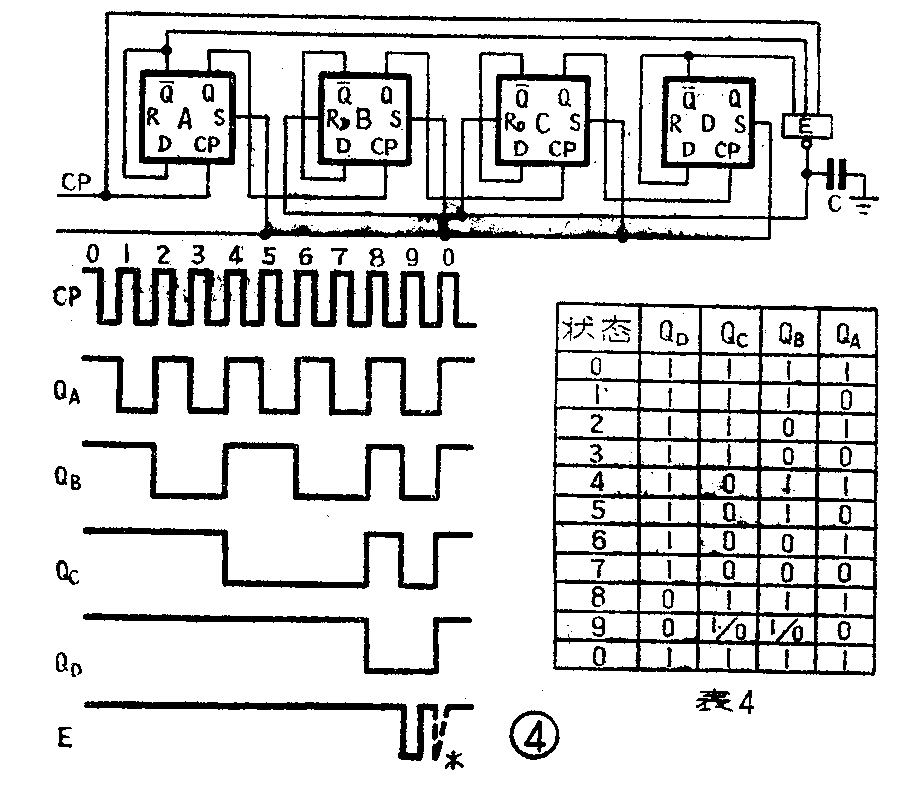

减法型十进计数器N-1=0110,将触发器A、D的Q-端和时钟脉冲接到与非门E的输入端,E的输出端接至触发器B、C的复位端R\(_{D}\),见图4。

加法型计数器的4个触发器在前8个时钟脉冲作用下逐次加1,第9个时钟脉冲使触发器成为A=1、B=0、C=0、D=1的状态(即N-1=1001),由于与非门E的存在。此时又输出一负脉冲,立即使B、C置位,状态即刻成为“1111”。这样,在第9个时钟脉冲作用下,出现短暂的“1001”状态后随即就使计数器处在A=B=C=D=“1”状态。第10个时钟脉冲使触发器全部回到“0”状态,完成了一次十进计数循环。而减法型计数器在第9个时钟脉冲的作用下将计数器置于“0000”状态。第10个时钟脉冲使其成为“1111”状态,完成一次减法型的十进计数循环。

图中电容C的作用是滤除由于触发器的传输延迟时间而产生的尖峰脉冲。如果不加电容C,当第10个时钟脉冲到达时,由于Q\(_{A}\)和QD的输出滞后于时钟脉冲一个tp的时间。因此与非门E的三个输入端瞬间仍可能都为“1”,使输出端产生一个尖脉冲*\(_{1}\),*1(见图3虚线所示波形)脉冲强制触发器B、C处于“1”状态,由于C处于“l”状态致使D也保持“1”状态不变,从而不能使4个触发器在第10个时钟脉冲作用下回到“0000”状态,第11个时钟脉冲使A由“1”→“0,B、C、D状态不变。第12个时钟脉冲到达后,同样又产生*\(_{2}\)脉冲(见图3虚线所示波形),*2脉冲仍强制触发器B、C保持“1”状态,使计数器无法进行计数。加上了电容C,对于*\(_{1}\)、*2这种频率的脉冲相当于短路,使它们不再对触发器产生影响,但加了电容C会使波形的前后沿变坏,影响电路的速度,所以电容C的大小一定要选择得当,本电路取C在几百~1000Pf左右。(王兆全)