在一些数字仪表和自动控制设备中,既使用晶体管等分立元件,又采用集成电路,尤其在自行设计的专用设备中,混合运用分立元件和集成电路的情况更为普遍。例如需要提供大的输出功率,或者要求较高的输出电平,就得求助于分立元件,而为了缩小体积、减轻重量、降低功耗,或者获得多种功能等方面,集成电路则有显著的优越性。在混合使用中,必然会发生一些新矛盾,其中一个基本问题,就是电子转换问题,也就是说怎样来协调它们各自的输出、输入电平问题。

从TTL集成电路输出给晶体管电路

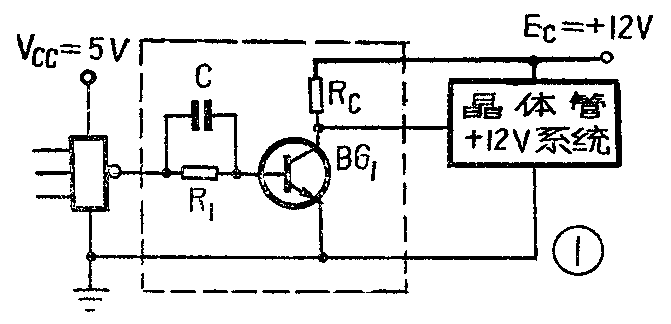

TTL集成电路的输出高电平V\(_{cg}\)=3.2V左右,输出低电平Vcd=0.32V左右。因此,用这个输出电平去控制晶体管的导通和截止,并不困难,电平转换线路也很简单,如图1所示,图中虚线框内部分为电平转换电路(以下各图同)。

当集成电路输出高电平时,通过电阻R\(_{1}\),向晶体管BG1提供足够的基极电流,使BG\(_{1}\)饱和,Ib≈\(\frac{V}{_{cg}}\)R1。R\(_{1}\)的数值要保证Ib足以使BG\(_{1}\)饱合。C是加速电容。当集成电路输出低电平时,BG1处于截止状态。

从BG\(_{1}\)的集电极引出的输出端接到下级晶体管系统。电平转换电路可以和晶体管系统用同一电源Ec,这就达到了电平转换的目的。实际使用时,在变换电平的同时还要注意相位的变化。

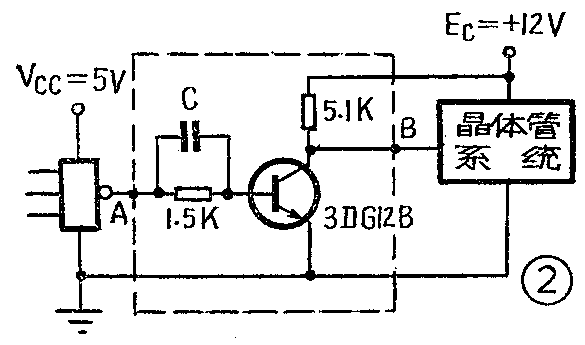

图2具体注明了元件数值,加速电容C一般取0~300pf,在一般工程控制电路中,对开关速度的要求不高,加速电容可以省去不用。

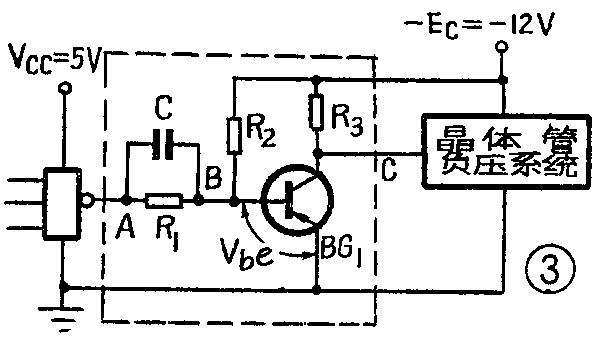

图3表示集成电路和晶体管负压电路系统(PNP型)连接时的情形。当集成电路输出高电平时,选择R\(_{1}\)、R2,使B点电位为正,或负电位的绝对值|V\(_{B}\)|小于PNP型晶体管BG1的射基极导通阈电压V\(_{bes}\),因而BG1截止,BG\(_{1}\)的输出电位Vc接近-E\(_{c}\),这时VB=V\(_{A}\)+R1R\(_{1}\)+R2(-E\(_{c}\)-VA)。当集成电路输出低电平时,使V\(_{B}\)为负,且|VB|>V\(_{bes}\),故BG1饱和导通,BG\(_{1}\)输出电位Vc接近0电平。当-E\(_{c}\)取-12V时,R1用2K,R\(_{2}\)用10K,R3用5.1K,就能满足上述要求。

从晶体管电路输出给TTL集成电路

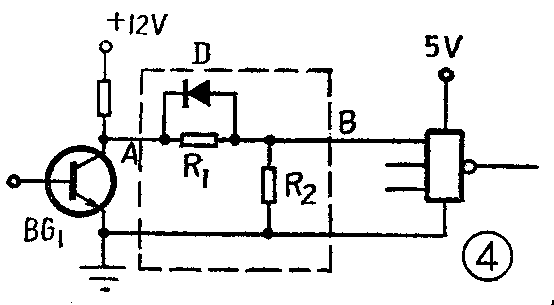

如果晶体管电路的电源电压+E\(_{c}\)(如+12V或+24V)比集成电路电源电压高,则连接时必须经过降压系统,如图4虚线框内所示。图中VB=\(\frac{R}{_{2}}\)R1+R\(_{2}\)VA。当晶体管BG\(_{1}\)截止时,晶体管的输出电位VA呈高电平,经过R\(_{1}\)和R2的分压,使B点电位满足1.8V≤V\(_{B}\)≤4.5V,即VB大于TTL集成电路的开门电平。当晶体管BG\(_{1}\)导通时,为保证TTL集成电路输入端VB为低电平,加接一只二极管D。为了尽量减少二极管本身的正向压降,可用锗二极管。这样的电平转换电路虽然简单,但抗干扰能力很差,而且能驱动的集成电路数量较少,图4大约能驱动3个集成电路。

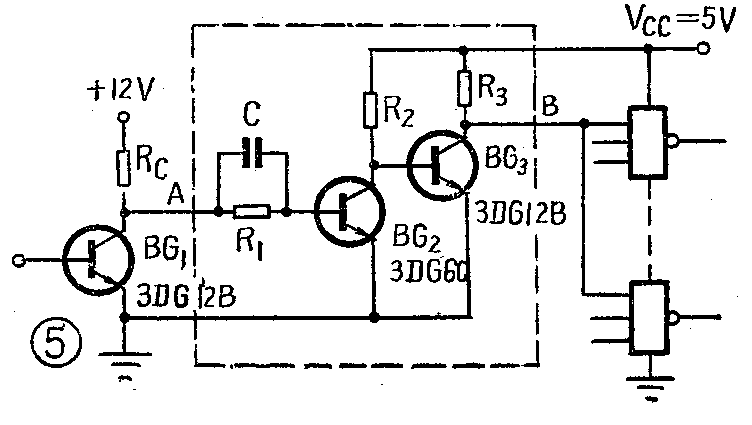

为了能驱动更多的集成电路,转换电路采用复合管,或者用两级反相器,如图5所示,这样的转换电路,能驱动10至20个集成电路。图中R\(_{1}\)的大小和Rc有关,大约R\(_{1}\)=(5~10)·Rc,这是为了使流过Rc的电流,大部分为BG\(_{1}\)的集电极电流,而BG2的基极电流只是其中的一小部分。图中电阻的数值可取R\(_{2}\)=4.7K,R3=5.1K,R\(_{c}\)=3K,R1=15K。

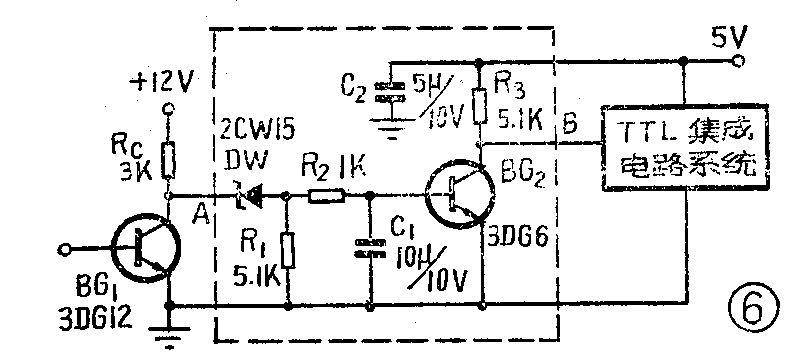

在工业环境中使用的数字仪表或自动控制系统,必须考虑抗干扰问题,这可采用图6所示的转换电路。R\(_{2}\)、C1组成积分电路,当晶体管BG\(_{1}\)的输出电位VA上升时,电容器C\(_{1}\)充电,电容两端的电压逐渐增大,只有当电容器两端电压增大到0.7V时,晶体管BG2才可能导通。BG\(_{2}\)导通时,转换电路输出端B点由高电位变成低电位。这样做,不仅可以提高门限电平,从而增强抗干扰能力,而且还可消除高频尖脉冲的影响。图6中的C2是为消除干扰用的。R\(_{c}\)的数值由前级电路确定,例如Ec=+12V,R\(_{c}\)=3K;Ec=+24V,R\(_{c}\)=5.1K。

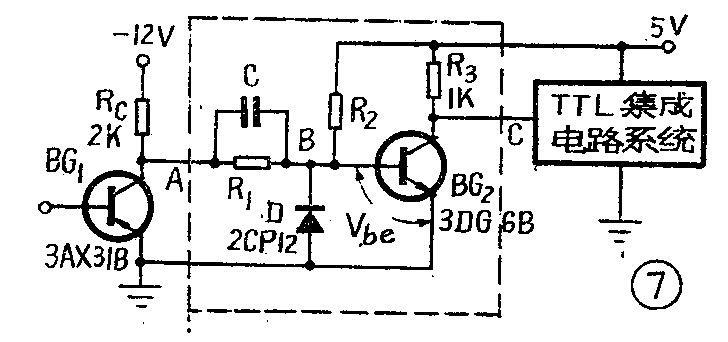

图7表示PNP型晶体管和TTL集成电路的电平转换。BG\(_{1}\)截止时,BG2的基极电位V\(_{B}\)<Vbes,所以BG\(_{2}\)也截止,BG2的输出电位V\(_{c}\)为高电平。BG1导通时,V\(_{B}\)>Vbes,BG\(_{2}\)也导通,输出电位Vc为低电平。这时V\(_{B}\)=VA+R\(_{1}\);R1+R\(_{2}\)(Vcc-V\(_{A}\)),式中VA为负值。R\(_{1}\)和R2可取2K和3K。二极管D(可用2CP12)起箝位作用,当BG\(_{1}\)截止时,VB被箝位于二极管D的正向压降0.7V左右,使BG\(_{2}\)不致截止过深,从而提高开关速度。

从TTL集成电路输出给MOS集成电路

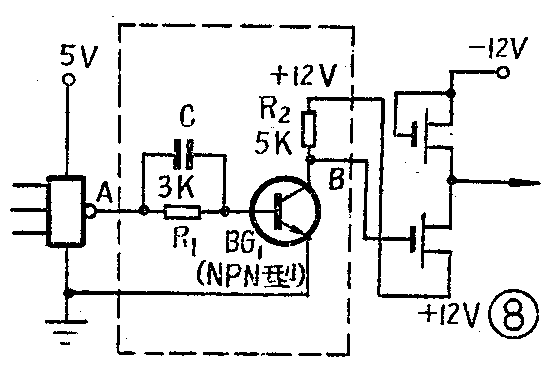

MOS集成电路的电源电压的选取有两种方案,一种是用-24V;另一种是用+12V和-12V两组电源。图8中的MOS电路就是用的+12V、-12V两组电源,这使转换电路变得很简单。因为BG\(_{1}\)的电源电压也是+12V,所以B点的输出电位恰好适合MOS电路输入电位的要求。可见,当整机内部混合使用TTL和MOS电路较多时,MOS电路的电源宜用+12V和-12V这种方案。

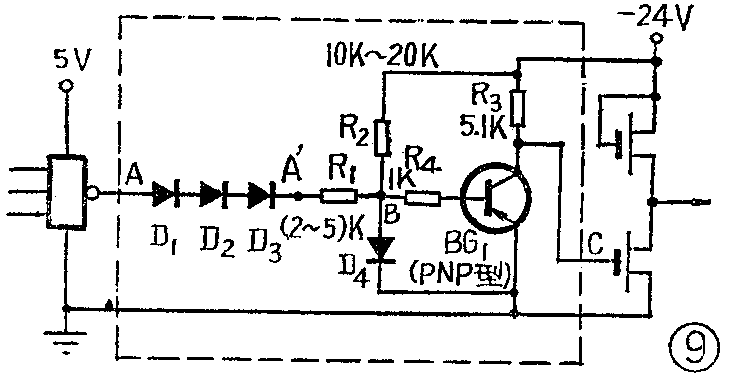

如果MOS电路用-24V电源,那么转换电路可用如图9所示。当A点为高电平(+3.2V)时,二极管D\(_{1}\)、D2、D\(_{3}\)导通,AA′间的压降等于三只二极管的正向压降之和,VA′约为+1.1V,只要适当选择R\(_{1}\)、R2,很容易使B点电位接近0V,由于D\(_{4}\)的作用,B点电位不会大于D4的正向压降,从而保证BG\(_{1}\)处于截止状态。当A点为低电平(+0.32V)时,二极管D1、D\(_{2}\)、D3仍导通,D\(_{4}\)截止,但由于D1、D\(_{2}\)、D3的正向压降,使V′\(_{A}\)被箝位为负值,适当选择R1、R\(_{2}\),便能保证BG1处于导通状态。从C点输出的电位恰好适合MOS电路的要求。显然,从TTL正电位输出连接到MOS负电位输入,转换电路需用PNP型晶体管,如3AX31C。D\(_{1}\)、D2、D\(_{3}\)可用2CP12,D4可用2AP4。

从MOS集成电路输出给TTL集成电路

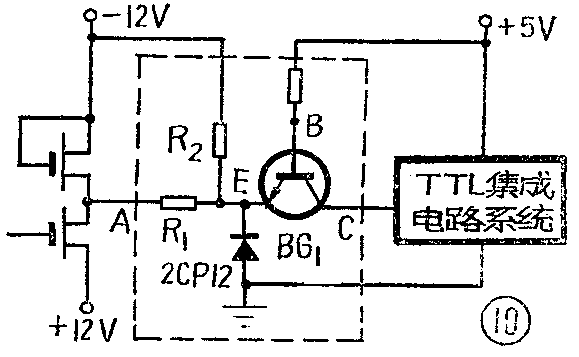

当MOS电路采用+12V、-12V两组电源时,从MOS到TTL的转换电路也很简单,如图10所示。当MOS电路输出低电平时,-12V电源经R\(_{1}\)和R2分压,使晶体管BG\(_{1}\)的发射极电位VE为负压,由于二极管D的作用,使V\(_{E}\)≈0.7V,因为晶体管基极电位为正,所以BG1导通,C点为低电平输出。当MOS电路输出高电平时,适当选取R\(_{1}\)和R2,使BG\(_{1}\)发射极电位VE高于基极电位VB,BG\(_{1}\)截止,这时,连接到TTL集成电路输入端的C点,可看作相当于悬空,也即相当于C点为高电平输出。

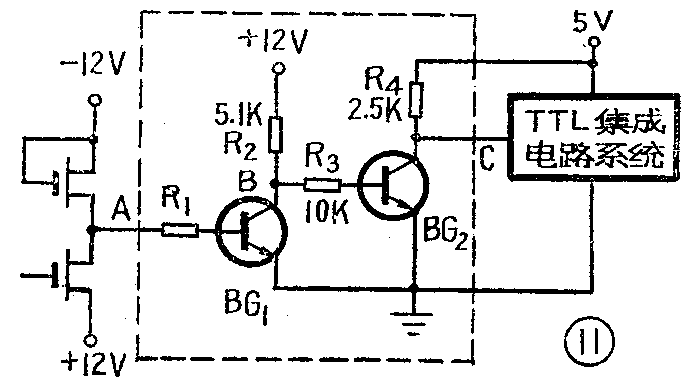

图11的转换电路用了两只晶体管,MOS电路输出端A为低电平时,BG\(_{1}\)截止,VB为高电平,保证BG\(_{2}\)有足够的基极电流,使BG2导通,C点输出低电平。当MOS电路输出端A为高电平时,BG\(_{1}\)导通,B点为低电平,使BG2截止,C点输出高电平,因为BG\(_{2}\)用5V电源,所以C点的输出电位可以适合TTL电路输入端的需要。

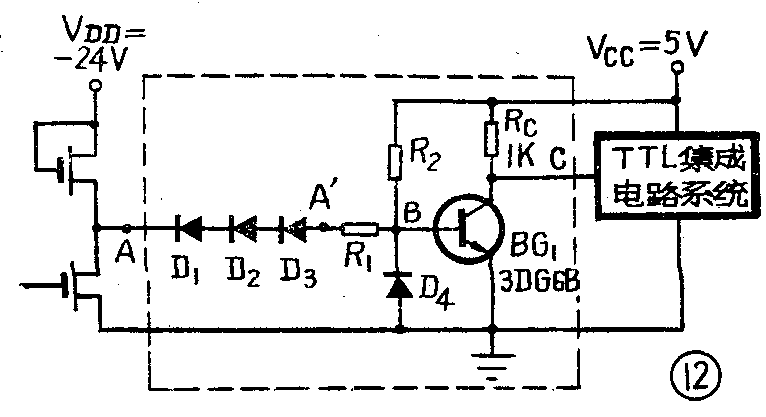

若MOS电路使用-24V电源,可采用图12所示的电平转换电路。当MOS电路输出为高电平(-3V)时,则因D\(_{1}\)、D2、D\(_{3}\)导通,三只二极管上的压降大约为3×0.7V=2.1V,A′点接近0电位,这时加上R1和R\(_{2}\)的分压作用,使B点电位为正,且VB大于晶体管的V\(_{bes}\),于是BG1导通,C点输出低电平。当MOS电路输出为低电平(-12V)时,则A′点电位在-10V左右,B点电位为负,BG\(_{1}\)截止,C点输出高电平。二极管D4的作用是当B点为负电位时,D\(_{4}\)导通,使VB<V\(_{bes}\),保证BG1截止,但截止深度不大,便于BG\(_{1}\)从截止到导通的迅速变换。图中D1、D\(_{2}\)、D3用2CP12,D\(_{4}\)用2AP4。

MOS电路和晶体管电路之间的电平转换问题,在上面介绍TTL电路和MOS电路之间的电平转换时,已经把这个问题顺便说明了。(天津市四十二中学 凌肇元)