MOS集成电路是由场效应管组成的单极型集成电路。与双极型集成电路(以双极型晶体三极管为基础的集成电路)比较,具有制作工艺简单、易达到高集成度、功耗小、抗辐射能力强、成本低等优点,所以在许多领域中得到了广泛的应用。

MOS集成电路一般可分为三大类:由P沟道场效应管组成的集成电路(P—MOS);由N沟道场效应管组成的集成电路(N—MOS);由P沟道和N沟道场效应管构成的互补电路组成的集成电路,又叫互补MOS电路(C—MOS)。

由于P—MOS电路的制作工艺最简单,所以目前使用较多的就是P—MOS电路。我们一般所说的MOS电路,常常指的就是P—MOS电路,下面讨论的也是P—MOS电路使用中的一些问题。

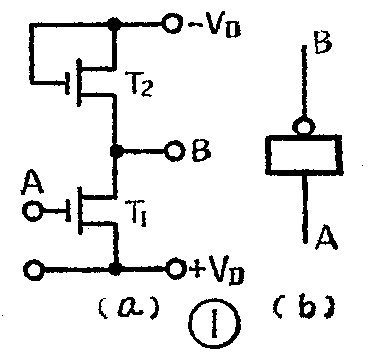

MOS反相器

MOS反相器是构成MOS集成电路的基本单元,由两只P沟道增强型场效应管组成。图1a是它的电路,b是逻辑符号。其逻辑关系与双极型反相器相同。即:输入“1”电平,输出“0”电平;输入“0”电平,输出“1”电平。图中A是输入端,B是输出端。T\(_{1}\)是反相管,也叫驱动管,T2是负载管。T\(_{1}\)的特点是互导较大,约在100~200μA/V之间,开启电压较小,约为4V。T2互导较小,约10μA/V左右,开启电压较大,约5~6V。

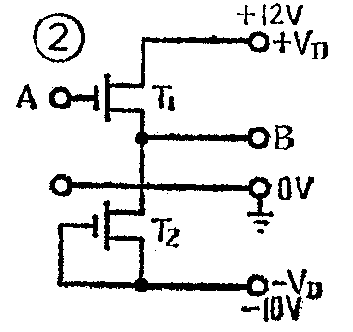

电源电压的选取有两种方法,第一种是+V\(_{D}\)=0V,-VD=-22V;第二种是+V\(_{D}\)=+12V,-VD=-10V。这两种方法各有特点,第一种只有一组电源,供电方便。第二种有两组电源,供电稍复杂些,但却有两个较明显的优点:

1.与外电路,如晶体三极管、双极型集成电路等,联接方便。

2.逻辑电平的规定比较习惯,线路设计、检查方便。

基于上述两种原因,线路设计中大部分采取第二种供电方式,如图2所示。

逻辑电平的规定见表1:

表1

供电方式 逻辑电平

+V\(_{D}\) -VD “1”电平 “0”电平

0V -22V ≥-3V ≤-12V

+12V -10V ≥+9V ≤0V

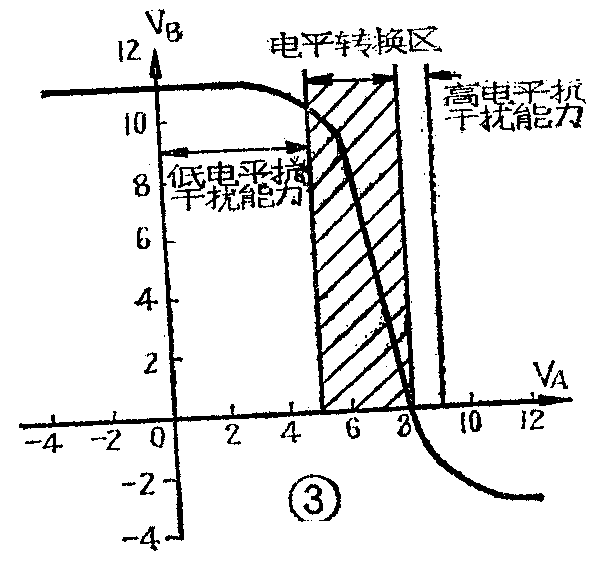

反相器的输入——输出电压特性见图3。从图3可看出输出电平是在输入电压+6V~+8V间转换的,这说明电路有较大的抗干扰能力,尤其是在输入为低电平的时候。

MOS电路反相器与双极型电路的反相器工作过程类似,但在使用中应注意下列几点:

1.是电压控制器件。

由于场效应管输入阻抗极高,输入电流几乎等于零,所以它不象双极型电路那样需要电流控制。

2.反相管的负载不是线性电阻,是漏—栅短接的场效应管T\(_{2}\)。

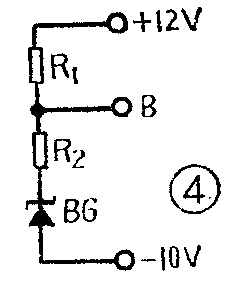

T\(_{2}\)的联接方式使得它的伏—安特性曲线呈非线性,与一般线性电阻的伏—安特性不同,这么做的原因是出于制作工艺的方便。因为在硅片上只制作场效应管一种器件比既有场效应管又有电阻要简单多了。当电路输入“0”电平时,反相管栅压VGS大于T\(_{1}\)的开启电压,T1导通,T\(_{2}\)也处于导通状态,反相器输出电压VB约在+9V以上。其等效电路示于图4,其中R\(_{1}\)为T1导通内阻,约为1.5千欧,R\(_{2}\)是T2的内阻,约在30千欧左右。BG的击穿电压等于T\(_{2}\)的开启电压,约等于6V。输入为“1”电平时,T1的V\(_{GS}\)小于开启电压,T1截止,T\(_{2}\)的VDS大大降低,因而T\(_{2}\)也接近截止状态。此时图4中的R1增至10兆欧以上,R\(_{2}\)也升至兆欧级,输出电压约为-4V左右。T2内阻的这种变化,在输出高电平时因其内阻减小,影响了高电平的升高。输出低电平时,因T\(_{2}\)内阻增大,影响了低电平的降低,这种情况使反相器的负载能力降低。

3.电流负载能力差。

双极型电路有较大的电流负载能力,MOS电路的电流负载能力比较低。输出高电平时,“拉”电流负载能力(输出电流的能力)约在0.3~0.8mA之间。输出低电平时,“灌”电流负载能力(输入电流的能力)一般不超过100μA。“拉”电流与“灌”电流负载能力相差很大,这是因为输出低电平时T\(_{2}\)处于微开启状态,内阻很大,通过它的电流稍大,T2上的压降就会造成输出电平超过规定的低电平数值。使用时应特别注意。

4.电容性负载能大大降低电路的工作速度。

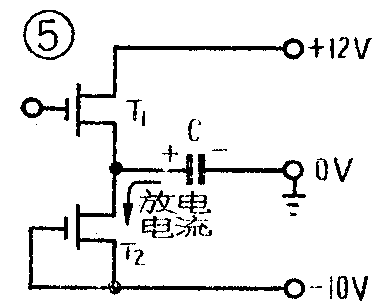

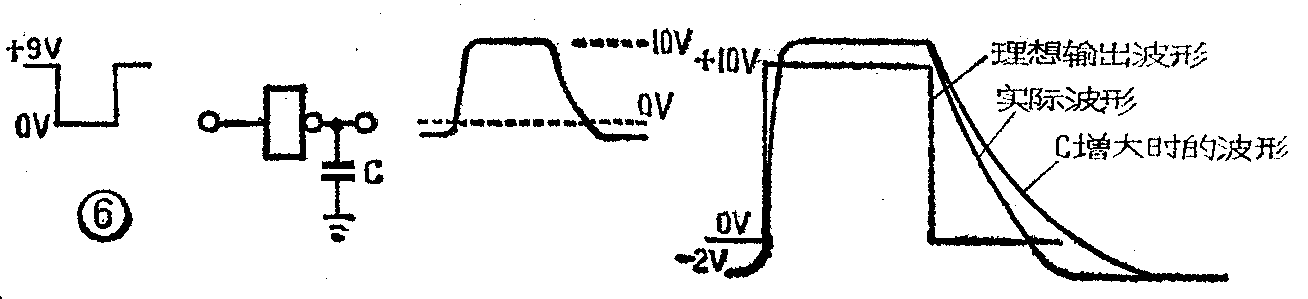

当输出端接有容抗性负载时,对输出脉冲的下降沿影响极大。从图5可明显看出,如输出端接有电容C,则当输出由高电平降至低电平时,因T\(_{2}\)的内阻较大,同时在电平的下降过程中又迅速增大,电容C的放电十分缓慢,大大延长了脉冲的下降时间,降低了工作速度。方脉冲通过反相器时,如输出端有容抗性负载,波形将变成图6所示的形状,输出脉冲的下降时间比上升时间约大一个数量级。P—MOS电路的这种缺点,使它只能工作在较低的频率下,一般不超过1兆赫。

MOS集成电路的产品中,一般没有单独的反相器,需要使用反相器时,往往都用“与非驱动器”来代替。

与非驱动器的使用

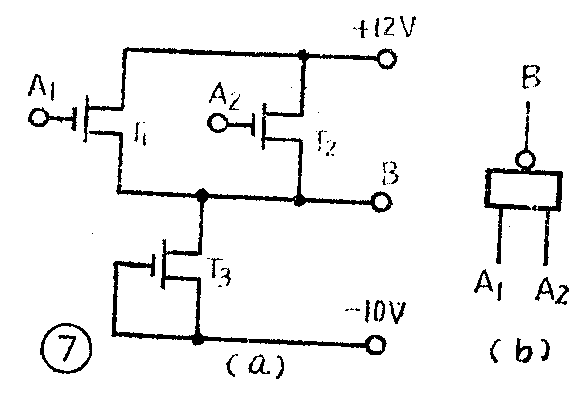

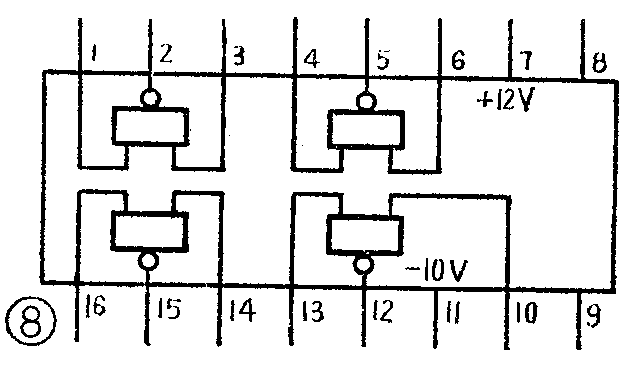

与非门是逻辑电路中应用最灵活的器件,它可以用来实现各种基本逻辑功能电路。MOS电路的与非门具有较大的驱动能力,所以又叫与非驱动器。图7a是一个两输入端的与非驱动器的电路,b是逻辑符号。它比反相器多了一个并联的反相管,工作特性与反相器相似,只是两个反相管T\(_{1}\)和T2同时截止时才输出低电平。其逻辑关系见表2。目前各厂生产的MOS集成电路型号不统一,下面以清华大学电子工程系生产的为例来介绍,图8是MOS—Q接线图。在一块电路中有四个独立的与非门,除电源线是共用的,四个与非门可各自独立使用。除MOS—Q型与非驱动器外,尚有MOS—3Q(四个三输入端与非门),MOS—5Q(两个五输入端与非门)等产品,使用方法与MOS—Q是一样的。

表2

A\(_{1}\) A2 B

0 0 1

0 1 1

1 0 1

1 1 0

MOS—Q型与非驱动器在逻辑线路中与双极型与非门功能是相同的,但在具体使用中应注意下列几点:

1.输入阻抗与箝位电阻:

同反相器一样,MOS—Q的输入阻抗是很高的,在产品说明书上一般规定为输入电阻大于1MΩ,电容小于2Pf。实际测量其直流输入电阻在70℃时都大于10MΩ,输入高电平时漏电流均在1μA以下。使用中有时需要对输入端箝位,箝位电阻的选择应根据输入电阻的大小和线路的需要来决定。一般情况下都希望箝位电阻大一些,以免加重前级的负载,但是箝位电阻过大会影响输入端电平,一般以选取在51KΩ~510KΩ间较合适,输入端漏电流大的应选小一些,漏电流小于5μA的可选用510KΩ的箝位电阻。

2.不使用的输入端的处理:

MOS电路的输入端是不能悬空的,因其输入阻抗大,输入电容小,悬空时,受空间电场影响会造成电平不定的情况,易产生误动作,所以不用的输入端必须使其箝位在“1”电平上。最简单的方法就是把不用的输入端在接联在+12V上,也可以与使用的输入端并联使用。

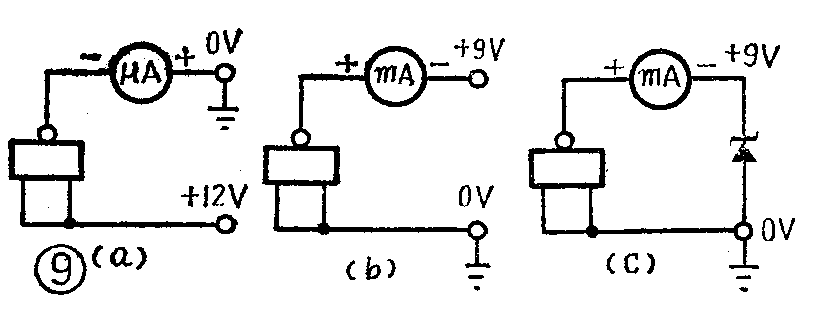

3.电流负载能力的简单测量:

采用图9的方法用万用表可以测出电路的电流负载能力,其中a是测量“灌”电流负载能力的方法,b、c是测量“拉”电流负载能力的方法。注意,要在MOS集成电路块加上电源电压后再按图9的联接方法测量。表3是几个MOS—Q型电路实际测量的结果。这种方法测出的结果,因电流表的内阻串接在电路中,测出的数值略小于电路的实际电流负载能力。

表3中可以看出,产品的参数离散度是较大的,因此先经过测量,使用时可根据不同的负载能力按线路的需要分配使用。

表3

电路编号 1 2 3 4 5

“拉”电流负载能力mA 0.8 0.6 0.75 1 0.85

“灌”电流负载能力μA 64 43 57 90 72

4.输出脉冲下降时间的估算:

输出脉冲由高电平降到低电平的时间主要由负载电容的容量决定,同时也与电路的“灌”电流负载能力有关。下降时间可以用下式进行估算:

t\(_{x}\)=3\(\frac{C}{i}\)

式中:t\(_{x}\):下降时间(由“1”电平降至“0”电平的时间),以μs为单位;C:负载电容容量,以Pf为单位;i:“灌”电流负载能力,采用图9测出的数据,以μA为单位。

由式中可看出,脉冲下降时间与负载电容容量成正比,与电路的“灌”电流负载能力成反比。使用时,对容抗性负载较重的部位应选择“灌”电流负载能力大的电路。

5.扇出系数:

由于MOS电路输入阻抗大,所以其扇出系数可以较大,不象双极型集成电路那样有严格规定。但是因输入电容的存在,当带动较多的MOS电路作负载时,脉冲的下降沿将被拖长,从而使工作速度降低。所以MOS电路的扇出系数应根据工作频率来考虑。一般以不超过5~10为宜。

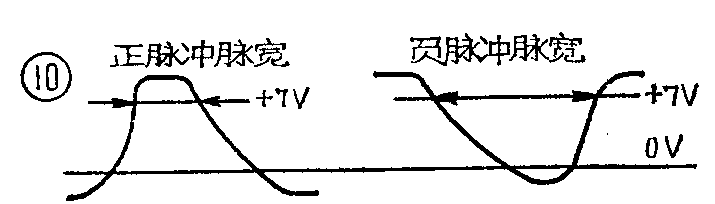

6.脉冲宽度的测量:

由于脉冲在线路中传递时其下降沿会拖长,因此用示波器测量脉冲宽度时应有其统一标准。参照图3可知,脉冲通过电路时,是在+6V至+8V之间进行转换的,所以测量脉冲宽度时应以+7V时的宽度为准。

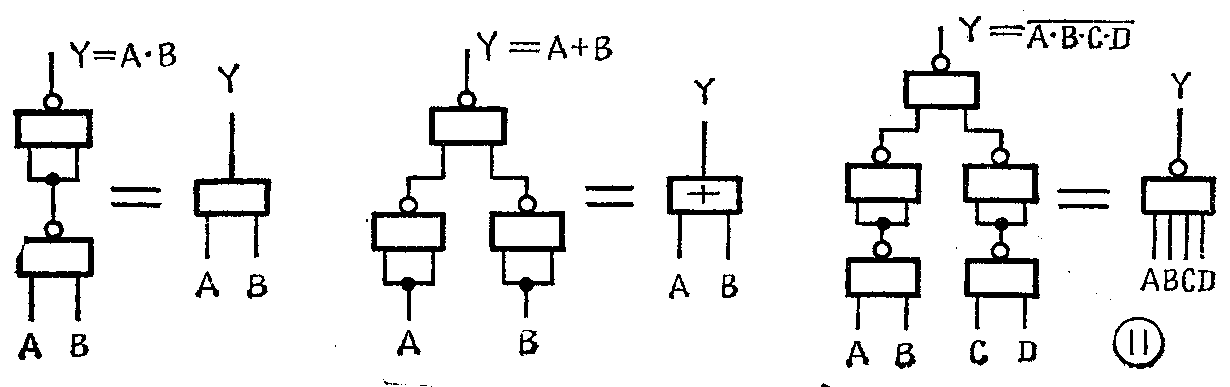

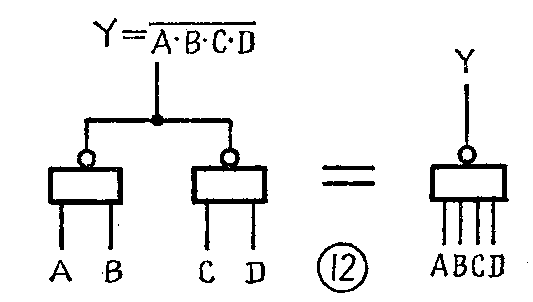

用与非门组成其它逻辑电路

用MOS电路与非门组成各种基本逻辑电路的方法与双极型集成电路使用的方法是一样的。图11是组成几种基本逻辑电路的例子。除此以外,还能利用MOS集成电路的特点,比较简单地构成多输入端的与非门,图12是其联接方法。这种方法因负载管的并联使用会造成输出高电平的降低,使用时应挑选输出电平较高的电路并联使用,而且不宜并联过多。

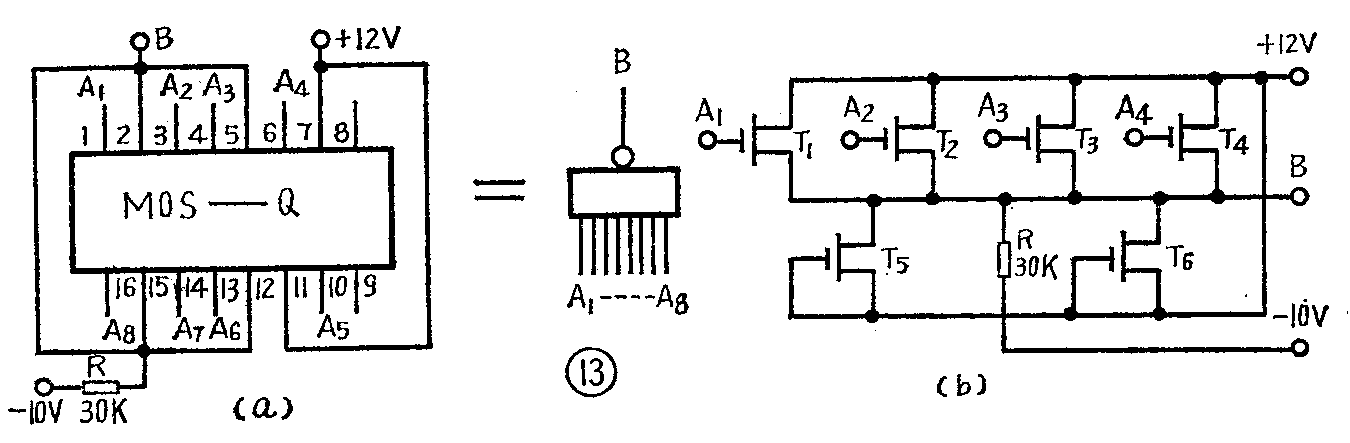

另一种组成多输入端与非门的方法见图13,a是联接方法,b是电路的简单说明。这种方法可以用一块MOS—Q型电路组成一个八输入端的与非门,输出电平幅度、负载能力、工作速度不仅不会降低反而能略有提高。从图13b可以看出,电路负载管(T\(_{5}\)、T6)的漏、栅极没接-10V,却直接接到+12V上,这样负载管的栅极对源极永远是正偏压,负载管也就永远截止了,负载管的功能由外加的负载电阻R代替了。这种方法没有图12电路的缺点,组成多输入端与非门是十分方便的。

与非门组成基本脉冲电路

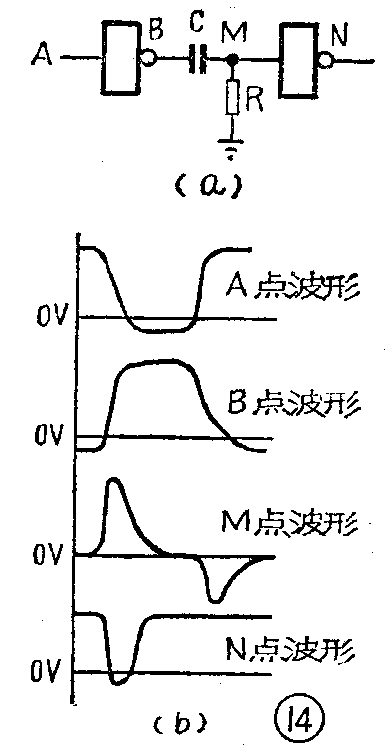

1.微分电路:

MOS电路组成的微分电路虽与双极型电路组成的微分电路联接方式相同,但考虑到MOS电路的特点,应注意下列几个问题,以图14的电路为例:

(一)要利用输入脉冲的上升沿进行微分。下降沿因下降时间太长,微分后幅度太小,不宜采用。

(二)接受微分脉冲的电路输入端要箝位在“0”电平上。可用100KΩ~510KΩ的电阻接在0V上。

(三)微分电容容量的选取与箝位电阻数值有关,其C·R值不应小于5μs。例如R=150KΩ,则C应大于40Pf。否则微分脉冲的幅度和宽度不易满足电路的要求。C也不宜选得过大,以免影响前级的工作速度。

(四)如需对某个脉冲的下降沿进行微分时,应先将其反相,使下降沿转换为上升沿,然后再微分。

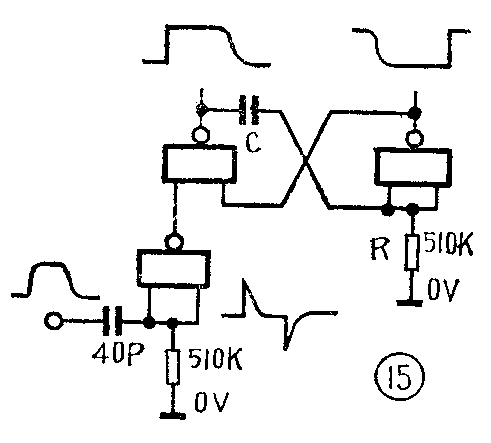

2.单稳触发器:

图15是由MOS—Q型与非门组成的微分型单稳触发器。它以负窄脉冲触发,图15中是以方脉冲前沿经微分、反相后得到的负窄脉冲触发的。输出脉冲宽度可按下式进行估算:

T≈0.3τ=0.3RC。

此式算出的结果偏差较大,对脉宽要求严格时,应当用示波器校准。

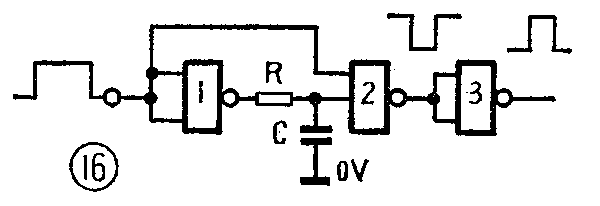

积分型单稳触发器如图16所示,它是以宽脉冲触发的。即输出脉冲宽度必须小于输入脉冲宽度电路才能正常工作。输出脉冲宽度取决于R、C的数值,并且受门1的“灌”电流负载能力的影响。R的数值不应大于510KΩ。

3.双稳触发器:

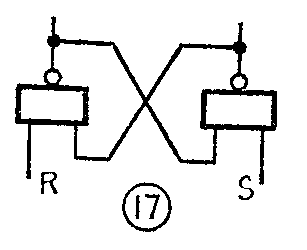

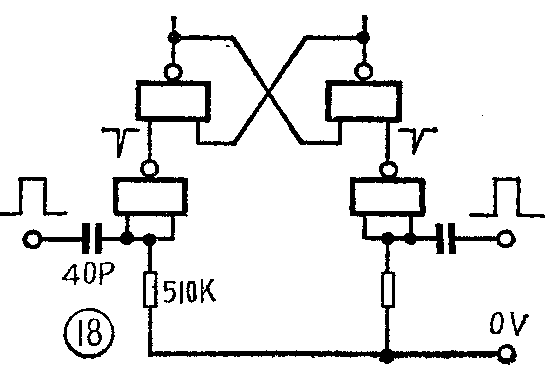

图17是R—S触发器的电路图。R端与S端应以“0”电平触发,平时应箝位在“1”电平上。如以微分脉冲触发,最好接成图18的电路,触发器将对应输入脉冲的前沿翻转。R—S触发器是一种置位—复位触发器,只能完成存储、记忆等功能,不能做计数器使用。

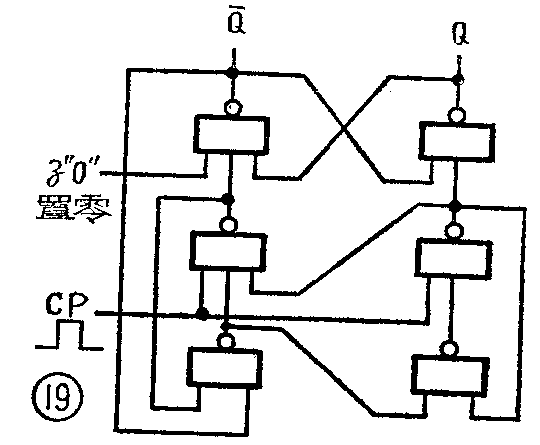

图19是由与非门联成的不对称维持阻塞触发器,这种触发器具有置位、计数、移位等功能。在MOS集成电路中有专用的维持阻塞触发器的产品,一般不用MOS—Q型与非门并接。

4.多谐振荡器:

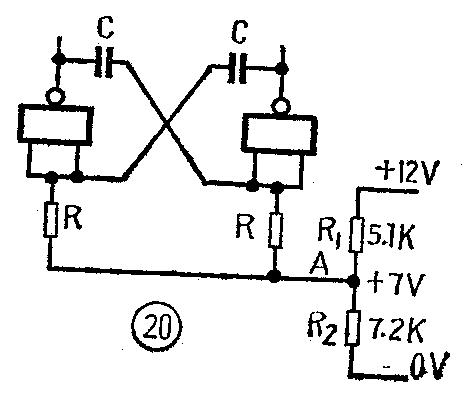

这类振荡器又叫无稳态触发器。图20是它的电路图。电路中A点电压调整在7~8V间电路就能可靠地起振,原因是当MOS电路与非门输入端电压在7~8V间时输出电平将呈现不稳定状态。参看图3可知,输入为7~8V间正是电路输入—输出特性曲线最陡的区域,加上电容C的交叉反馈,电路就很容易起振。振荡频率由R、C的乘积和MOS—Q的参数决定。一般R可选在200KΩ~510KΩ之间,C选取在20~1000Pf间。最高振荡频率在200KC左右。振荡周期T约在0.5~0.8R·C之间。

5.环形振荡器:

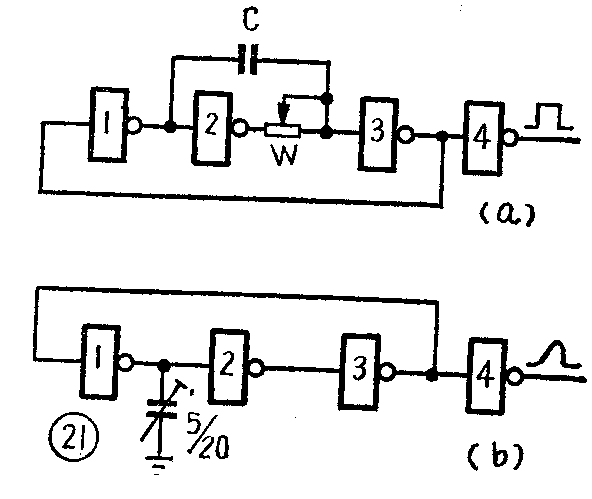

同双极型集成电路一样,MOS集成电路与非门也可以很方便地组成环形振荡器。图21就是环形振荡器的电路。图中,门3的输出连在门1的输入端上,讯号经过奇次(图中为三次)反相,反馈至输入端,电路呈现不稳状态并产生振荡。振荡频率由讯号传输过程中的延迟时间来决定。图21a中,C可选择大于100Pf的电容,W用510KΩ以下的电位器,用以调节振荡频率。最高振荡频率能达到200千赫。图21b最高振荡频率可达1兆赫以上,但波形稍差。

MOS电路使用中的注意事项

1.虽然MOS集成电路输入端有保护用稳压二极管,但是栅穿的可能性还是存在的。为避免栅穿,应注意下列几点:

(一)焊接用的电烙铁要接地线,最好用20瓦内热式烙铁。

(二)所有测试仪表,如脉冲讯号发生器、示波器、稳压电源等,都要良好接地。

(三)焊接用的工作台不要铺塑料板、橡皮垫等易带静电的物体,也不要用塑料袋等包装电路。

(四)焊接时切勿过早拆开包装的铝箔,应拆开一块立即焊一块。

2.由于MOS电路输入阻抗高,电路引出线间的轻微漏电也会造成工作失常。为保证绝缘良好应做到下列几点:

(一)焊接时不能使用焊油,最好用带松香的焊锡丝。

(二)焊接的电路板上要保持清洁、干燥。不能用出汗的手摸。

(三)MOS电路多数采用扁平封装,引出脚间距离很小,焊接时应十分小心,焊锡不要用得过多,以免引出脚间短路。

3.MOS电路电流负载能力低,容抗性负载对工作速度影响极大,设计、安装过程中应尽量减小容抗性负载。排板、布线时要考虑引线电容的影响。讯号须长距离传送或负载较重时,应考虑加晶体三极管驱动级。(刘铁城)