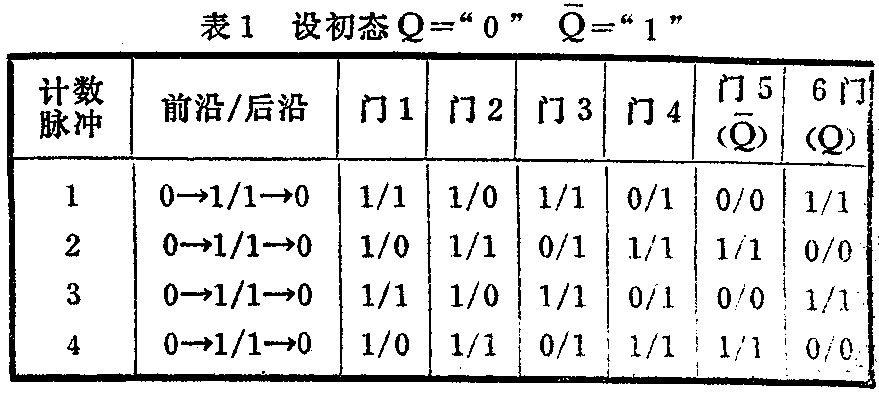

在小型数控装置和数字化仪表中,常常采用由单片集成电路“与非”门通过外部连线搭接成的计数触发器。图1是一种典型的由六个TTL与非门构成的“维持——阻塞触发器”,简称WZ触发器。现在介绍这种触发器的工作原理和由它组成的可逆计数器。

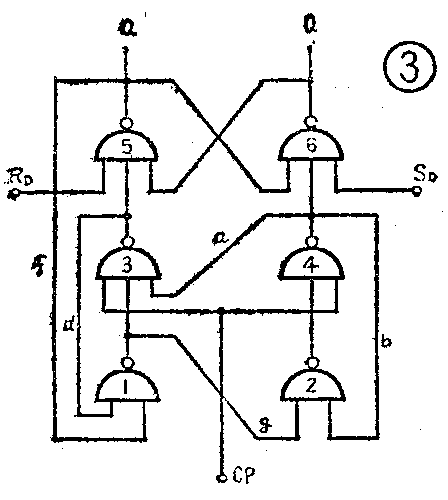

图1中的与非门5和6组成触发器的基本部分——RS触发器,再加上两个门电路作为导引电路,可以组成简单的计数触发器,如图2所示。设图2中Q=“0”、Q-=“1”,则通过导引线E和F,使门3的输入有“0”,门3被封住。当计数脉冲到来,CP=“1”时,计数脉冲将引入门4。当下个计数脉冲到来时,因Q=“1”而Q-=“0”,故门4被封锁,计数脉冲将引入门3。

图2的线路虽然起到了导引作用,但如果输入脉冲较宽,触发器的翻转又很快,当CP仍为“1”而Q与Q-已改变了状态,这时就会发生连续不断的翻转,也就是在一个计数脉冲作用期间引起触发器的多次翻转,这叫做“空翻”。空翻现象使计数触发器无法正常工作。

为了“维持”一定的稳态,“阻塞”空翻现象,产生了由六个单与非门组成的WZ触发器。这是一种有自锁作用的双稳态计数触发器。输入脉冲的前沿使触发器翻转,后沿为下次翻转作准备。

为了说明WZ触发器的工作过程,设起始状态为Q=0”,Q-=“1”。通过图1中导引线e和f,使门2封住,输出为“1”。当CP=“0”时,门3和门4均因输入有“0”而输出为“1”,使门1因输入全“1”而输出为“0”。门1输出为“0”就封住了门3,使计数脉冲只能导引入门4,这就起到了正确导引作用。

当第一个计数脉冲前沿(即由“0”→“1”)到来时,门4输出负信号,作用在RS触发器的置“1”端(门6的输入端),使触发器置“1”,翻转为Q=“1”、Q-=“0”。

值得注意的是,仅仅依靠e、f两条线导引计数脉冲,还不能保证触发器正确而可靠地计数。当Q端由“0”→“1”时,会通过e线反馈到门2的输入端,若不加b线,就会使门2翻转,从而引起触发器空翻。为了使Q端电位的变化不影响置“1”的稳定状态,我们把门4输出端的低电位,通过b线连到门2的输入端,封住门2,所以b线叫置“1”维持线。

与此同时,Q-由“1”→“0”时,将通过f线反馈到门1的输入端,使门1由“0”→“1”,这时,若没有a线的“0”电平保持门3输出的“ 1”电平,则门3将会因“输入全‘1’而输出为‘0’”,使门5又翻回“1”,使触发器置“0”。所以a线叫做置“0”阻塞线。

这样自锁以后,计数脉冲作用期间,CP=“1”时,不会因Q的翻转而引起空翻,当CP=“0”时,门3、门4均为“1”,Q和Q-保持原状态。门1输出为“1”,门2输出为“0”,封锁了门4,为下一个脉冲来时导引入门3准备好了触发条件。

由于图1的电路是完全对称的,所以当触发器由“1”→“0”的置“0”过程中,d线起维持置“0”作用,C线起阻塞置“1”作用,分别把d线叫做置“0”维持线,把c线叫做置“1”阻塞线。

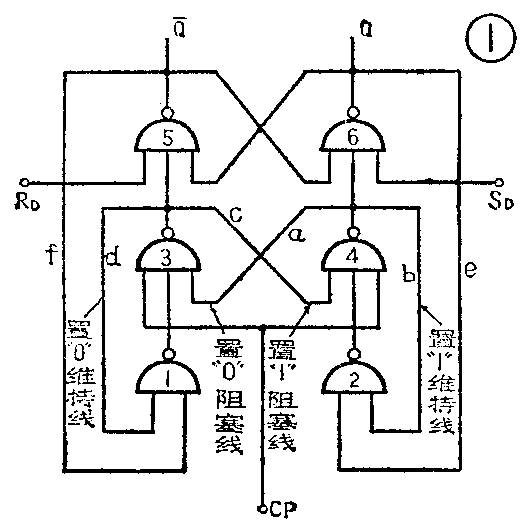

人们在实践中对这种对称形式的WZ触发器进行了简化,如图3所示,叫做不对称WZ触发器。二者的区别在于图3用线g代替了图1中的c线和e线。为什么能用一根线代替两根线呢?e线是从Q端直接反馈到门2输入端,而g线是Q端经门5反相(Q-始终与Q反相)又经门1反相(门1的另一输入线当CP=“0”时因门3输出为高电平而为“1”)后反馈到门2输入端的,作用效果相同,故g线可代替e线。至于还可代替置“1”阻塞线c的道理为,当门3输出为“0”时,门1被封住,输出为“1”,经g线使门2输出为“0”,于是封锁了门4,阻塞了置“1”脉冲的产生,所以g线也称为代置“1”阻塞线。

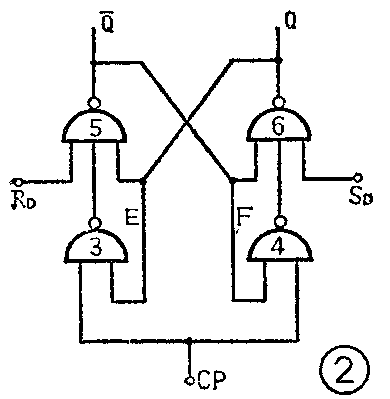

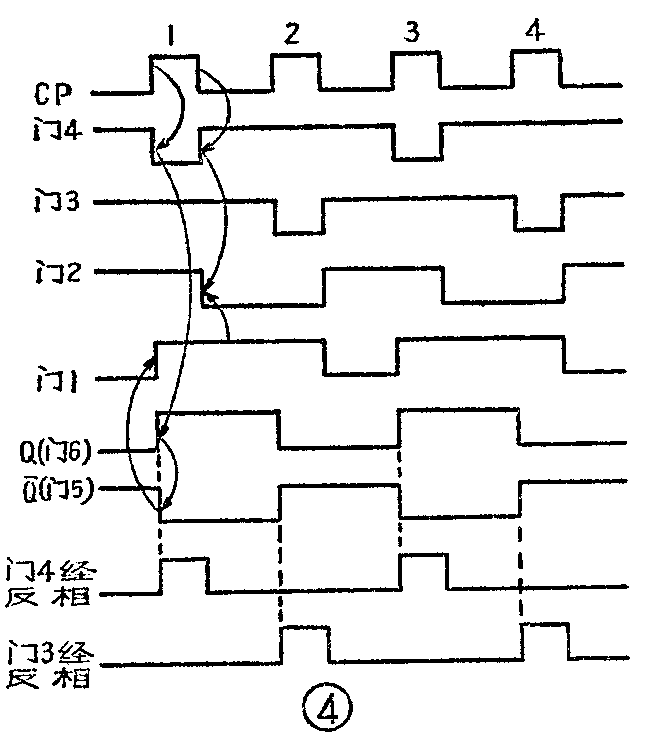

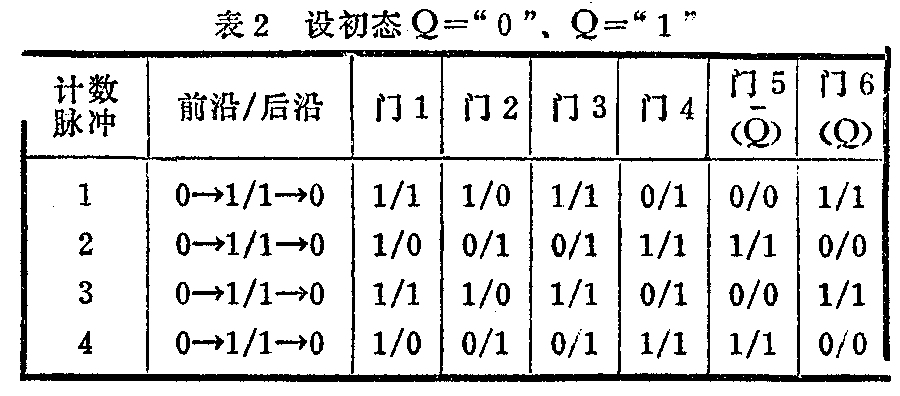

不对称WZ触发器的工作过程可用图4所示的波形图来说明,表2表示它的直流触发电平的逻辑变化关系。从图4和表2可以看出:

①CP端每输入一个计数脉冲时,用正脉冲前沿触发,使Q和Q-交换一下状态,即翻转一次;

②每输入二个计数脉冲,门3就输出一个和CP等宽的负脉冲信号,起“逢二进一”作用,即每逢CP为2、4、6……时,门3输出负脉冲;

③门4则在CP为1、3、5……单数时,输出和CP等宽的负脉冲;

④比较一下门4经反相后的波形和门Q的波形,上升沿在同一时刻;同样,比较一下门3经反相后的波形和门Q-的波形,上升沿也在同一时刻(此处都忽略门电路自身的延迟时间)。

这里还需要说明WZ触发器的二个特点,即它的置“0”端和进位端。

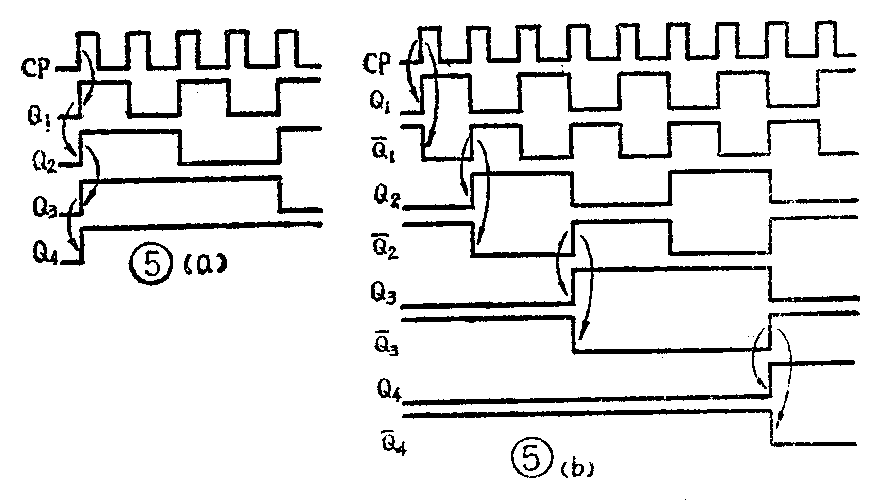

进位引出方式和触发方式有关。如果用脉冲后沿触发,则从Q端输出,利用Q的下降沿;如果用脉冲前沿触发,则从Q-端输出,利用Q-的上升沿,以避免“一翻全翻”的现象(见图5)。

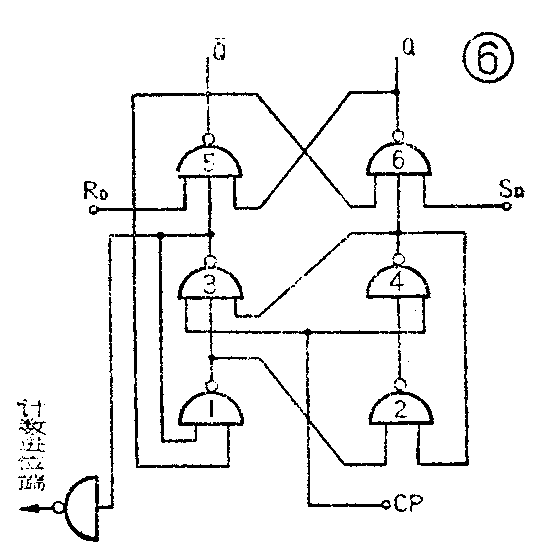

图6画出了不对称WZ触发器的置“0”端和进位端。为什么触发器输出给下一级的进位端,不用过去习惯使用的Q-端(正脉冲前沿触发),而改用门3再经反相输出呢?这是因为,一方面门3输出经反相后的正脉冲前沿,恰好和Q-的上升沿同时,用门3反相后作进位脉冲,能达到从Q-引出进位端同样的效果;另一方面,门3反相后的脉冲宽度和CP脉冲等宽,所以当CP=0时,门3反相后为低电平,使下一级触发器的输入端在没有输入脉冲时始终为“0”状态,保证这一级触发器的门3、门4平时为“1”电平。这时,要使WZ触发器置“0”,只需要在门5的一个输入端(即RS触发器的置“0”端)加负脉冲即可,这就使置“0”连线变得较为简单。但是如果从Q-端输出给下一级的话,当Q-为“1”时,使下一级触发器输入为“1”,这意味着下级触发器的门4输出有可能为“0”(使RS触发器置“1”);这时要确保整个触发器置“0”,单向门5输入一个负脉冲,条件还不充分,必须同时将置“0”脉冲输给门4和门1,如同D触发器一样,这当然会使置“0”连线变得复杂。这就是我们为什么用门3经反相输出代替Q-作进位端的道理。可见,这里综合考虑了进位和置“0”(复位)两个问题。

通过以上分析,使我们对WZ触发器的基本原理和逻辑功能有了初步的了解,在这个基础上,我们就可以进一步研究用WZ触发器组成的可逆计数器。

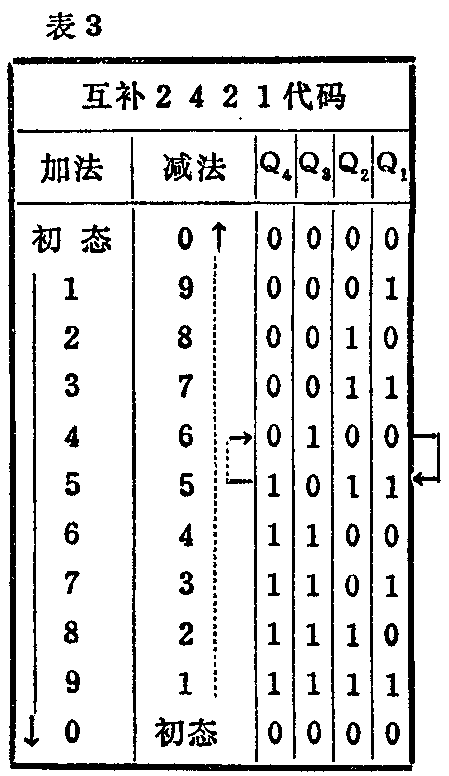

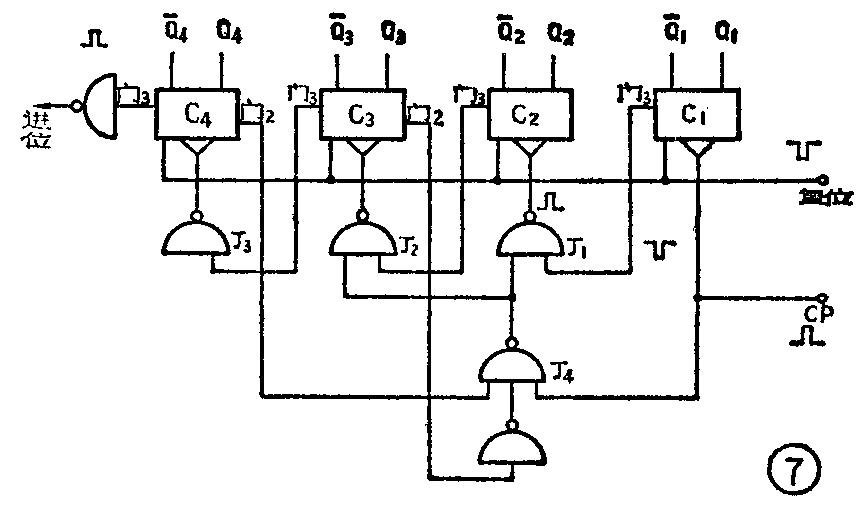

可逆计数器是一种既能进行加法计数又能进行减法计数的计数器。关于加法计数器,已经在上篇作过介绍。上篇图10所示的互补“2421”代码加法计数器,十个数字的状态变换顺序如表3第一行所示,当采用WZ触发器时,其逻辑图如图7所示。在图7中,从门3经反相引出进位信号,输给下一级CP端,复位脉冲则从门5的一个输入端引入。反馈线则自门2输出端引出,从图4看出,门2和Q-端输出波形相似,但门2随CP下降沿跳变,所以更适合于作反馈输出端。

减法计数器的基本要求是,每接收一个计数脉冲,就从计数器里减掉一个数字,当采用互补“2421”代码时,每减一个数字的状态变换顺序如表3第二行所示,按自下而上的顺序变换。在二进制中,因为1-1=0,故当初始状态为“1”时,若接收一个减法计数脉冲,就减去“1”,变成“0”;因为0-1=1,故当初始状态为“0”时,若接收一个减法计数脉冲,本位就变“1”,并向高位发出借位脉冲信号,实际是10-1=1。表3中初态为“0000”,接收第一个减法计数脉冲后,C\(_{1}\)变“1”并向C2借位,使C\(_{2}\)也变“1”并向C3借位,C\(_{3}\)、C4也是这样,结果形成“1111”,并向前一位计数器发出借位脉冲信号。这个状态,恰好是加法十进制计数器里的数字9。这表示,在十进制中10-1=9。当接收第二个减法计数脉冲后,C\(_{1}\)由1变0,无需借位,计数器呈“1110”。这个状态,恰好是加法十进制计数器里的数字8。这表示,在十进制中9-1=8。当接收第三个减法计数脉冲后,C1由0变1,向C\(_{2}\)借位,使C2由1变0。整个状态变为“1101”。这个状态,恰好是加法十进制计数器里的数字7。这表示,在十进制中8-1=7。其余可依此类推。

由此可见,根据减法计数器需要借位这个特点,减法计数器的借位脉冲引出端和加法计数器恰好相反。当用正脉冲前沿触发时,不是从Q-端引出而是从Q端引出。因为当触发器由“0”变“1”时(这时需要借位),Q端产生的正跳变正好作为向高位触发器借位的借位信号,而Q-端这时产生的是一负跳变,对前级触发器翻转不起作用。当用WZ触发器作减法计数时,采用正脉冲前沿触发,借位脉冲引出端引自门4再经反相输出,连到下一级触发器CP端,其道理同前所述。

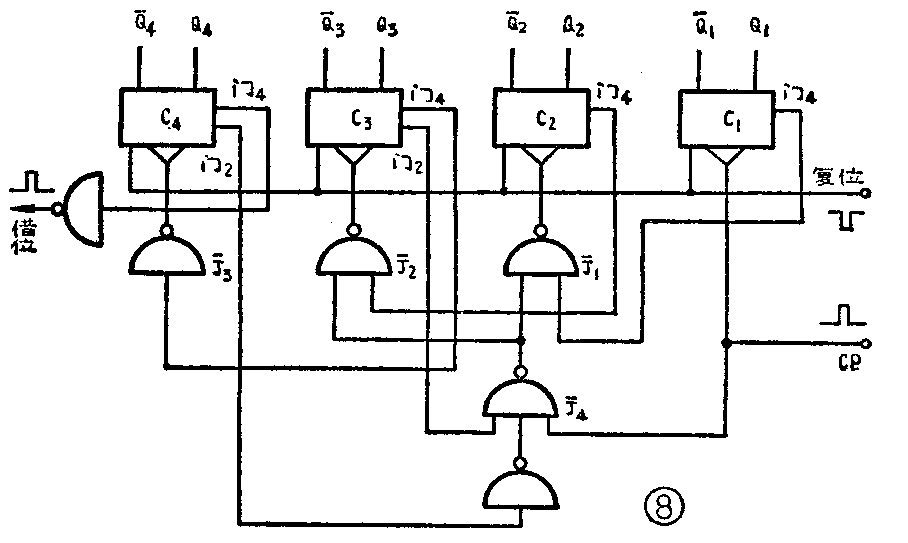

互补“2421”代码十进制加法计数器的关键在于由4到5(由“0100”到“1011”)的跳变。同样,互补“2421”代码十进制减法计数器的关键在于由“1011”到“0100”的跳变(从表3中看出这相当于减法计数器的第5个计数脉冲到第6个计数脉冲)。为了实现这种跳变,减法计数器的反馈控制门如图8所示。在第6个减法计数脉冲末到前和第6个计数脉冲后,均按正常的二进制减法计数,在这些时候,与非门J-\(_{4}\)因总是“输入有0,输出为1”,J-1、J-\(_{2}\)、J-3只起反相器的作用,将来自触发器门4的信号反相后输出给下一级触发器。但一旦出现“1011”状态,这时Q-\(_{4}\)=“0”、Q-3=“1”(注意这在十种状态中只有一次机会),C4的门2输出为“0”,经反相连到J-\(_{4}\)输入端,C3的门2为“1”并且第6个减法计数脉冲前沿到来,J-\(_{4}\)就变成“输入全1,输出为“0”,又因为WZ触发器在无信号输入时,门4、门3输出总为“1”电平,致使第6个减法计数脉冲前沿一到,J-1和J-\(_{2}\)就发生正跳变,从而造成C2和C\(_{3}\)翻转。又因C3由“0”变“1”,使C\(_{4}\)跟着翻转。同时,输入信号使C1也翻转。结果,第6个减法计数脉冲后的状态变成“0100”。

由初态“0000”进入第一个减法计数脉冲,变成“1111”状态时,十进制计数器要向高一级十进制计数器借位,这个借位信号是由C\(_{4}\)的门4经反相后引出的,送到高一级十进制计数器的输入端。

在这里再提醒一句,每当WZ触发器由“0”变“1”时,触发器的门4经反相这一端,有正脉冲出现(见图4),宽度同输入脉冲,而门3经反相那一端没有变化;当触发器由“1”变“0”时,触发器门4经反相这一端没有变化,而门3经反相那一端有正脉冲出现,宽度同输入脉冲。所以每当触发器由“0”变“1”时,触发器门4反相这端发出借位脉冲,每当触发器由“1”变“0”,触发器门3反相那端发出进位脉冲。

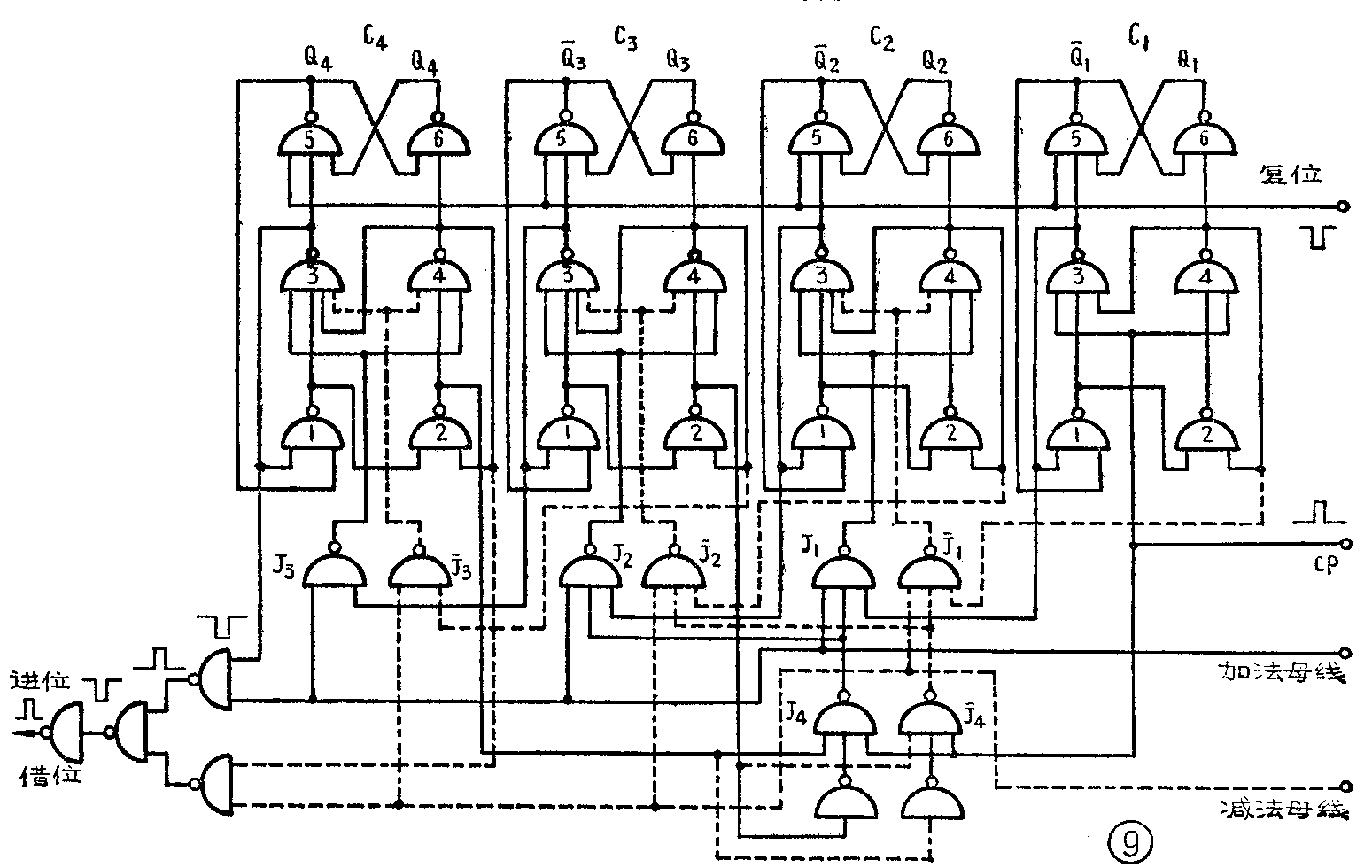

可逆计数器需要把图7和图8所示的加法计数器和减法计数器合并在一起,用同一组触发器。做加法时,减法反馈门不起作用,仅加法反馈门起作用,完成加法计数的动作,做减法时,加法反馈门不起作用,仅减法反馈门起作用,完成减法计数器动作。为了达到这个目的,根据与非门电路的特点,用一根加法母线和一根减法母线来控制。如图9所示,做加法计数时,加法母线置“1”电平,减法母线过“0”电平。故J-\(_{1}\)、J-2、J-\(_{3}\)被封住,输出始终为“1”电平,这时可逆计数器等于一个加法计数器(计数原理与加法计数器相同)。做减法计数时,减法母线置“1”电平,加法母线置“0”电平,J1、J\(_{2}\)、J3被封住,输出始终为“1”电平,这时可逆计数器等于一个减法计数器,计数原理与减法计数器相同。加、减法进位和借位门是由与非门组成的“或”门,再加一级反相器,进位脉冲和借位脉冲从同一处引出。

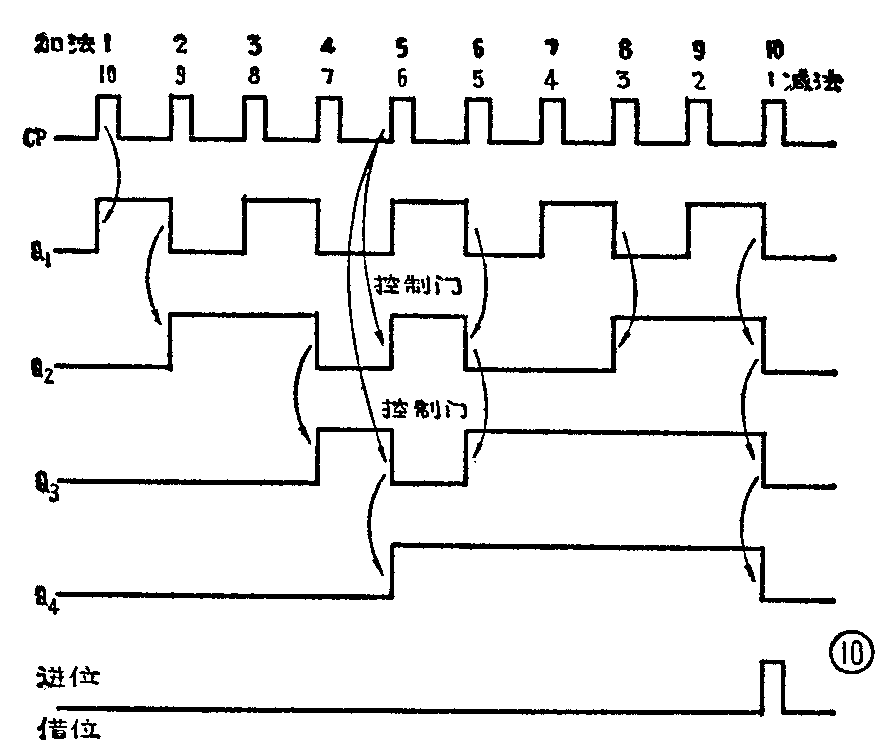

图10是WZ触发器组成互补“2421’十进制可逆计数器各级波形图。进位信号产生于加法的第10个脉冲,借位信号产生于减法的第1个脉冲,设起始状态为“0000”。

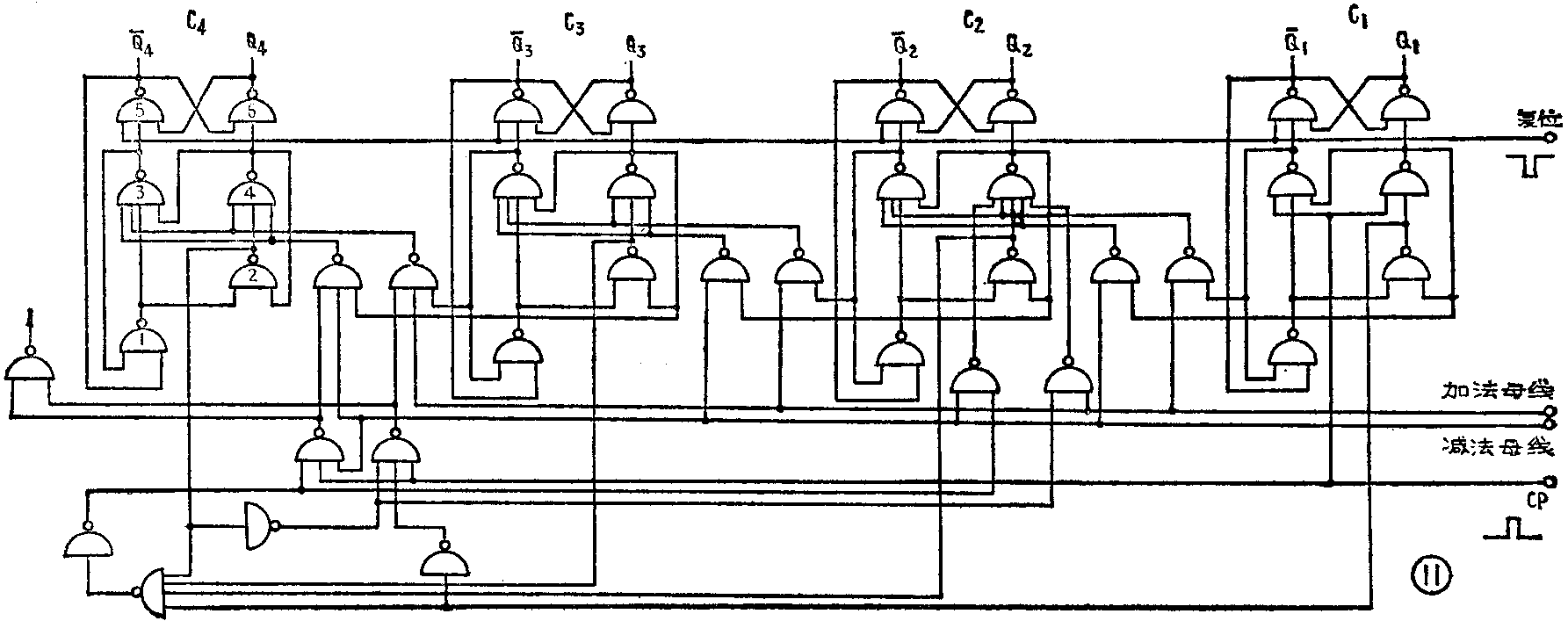

组成可逆计数器的方案有很多种,譬如用WZ触发器也可以组成“8421”代码可逆计数器如图11所示,读者可以自行分析。

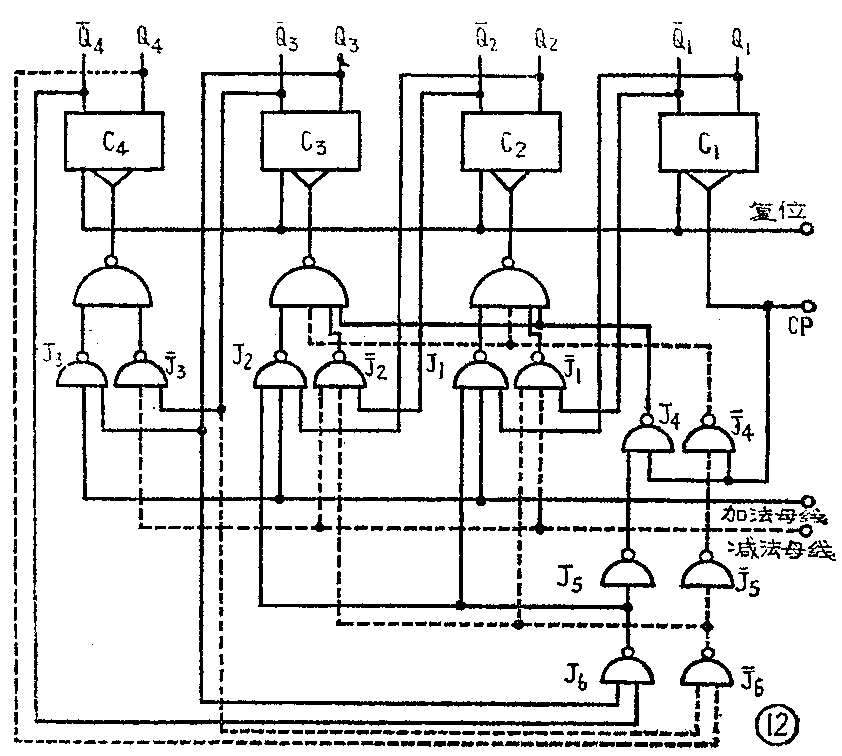

图12所示是由JK触发器组成的互补“2421”代码可逆十进制计数器,这时的JK触发器接成RS触发器使用。它的工作原理,同样是通过加法、减法母线以控制加法计数和减法计数。由于JK触发器没有WZ触发器的门3、门4交替输出进位信号和借位信号这一特点,而利用Q和Q-输出。而且因为JK触发器用后沿触发,进位端从Q引出,借位端从Q-引出。

最后说明一下,本文所介绍的计数器都属于异步计数器,各级触发器的翻转,由低位逐次向高位依靠进位脉冲信号的传递来实现。其缺点是计数速度较慢。在要求高速度计数时,可以采用同步计数器,同步计数器的计数脉冲同时输入各级触发器,每计一个数,只要求一级触发器的翻转延迟时间,这就提高了计数速度。(天津市四十二中学 凌肇元)