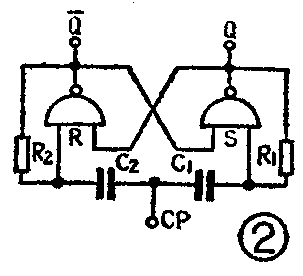

触发器是计数器的基本单元,计数器就是运用触发器的功能来实现运算和计数的。两只与非门集成电路可以组成一个集成电路双稳态触发器,每只与非门相当于一只反相器。图1表示这种基本触发器的逻辑图、逻辑符号和真值表。它的两个输出端Q和Q-,分别交叉耦合到另一只与非门的输入端,如同分立元件双稳态电路每级反相器的集电极输出,交叉耦合到另一级反相器的基极输入一样。不同之处,由与非门组成的触发器,两组输入端分别由几个输入端组成与门,使具备更多的功能,称为R端和S端,这种触发器也叫RS触发器。

RS触发器的两只与非门,一面互相对立,一面互相依存,一只门处于开门状态,促使另一只门处于关门状态,这后一只门的关门状态又反过来保证了前一只门处于开门状态,它们各以对立着的方面为自己存在的前提,处于相对统一的状态,于是就形成所谓“稳态”。显然,这种稳态是有条件的、相对的、可变动的,在外界信号触发下,稳态被破坏,电路发生转化,各向着对立面所处的状态转化了去。

RS触发器具有如下功能:

(1)当S=“1”、R=“0”时;Q=“0”、Q-=“1”。即S输入端全为高电平,R有一端或几端为低电平,触发器就呈“0”状态,所以把R输入端叫置“0”端或复位端。显然,不管触发器原来处于什么状态,只要R中任一端输入低电平或碰一下地,触发器就呈“0”态。

(2)当S=“0”、R=“1”时;Q=“1”、Q-=“0”。即R输入端全为高电平,S有一端或几端为低电平,触发器就呈“1”状态,所以把S输入端叫置“1”端或置位端。

(3)R=S=“1”时,Q保持原状态不变。

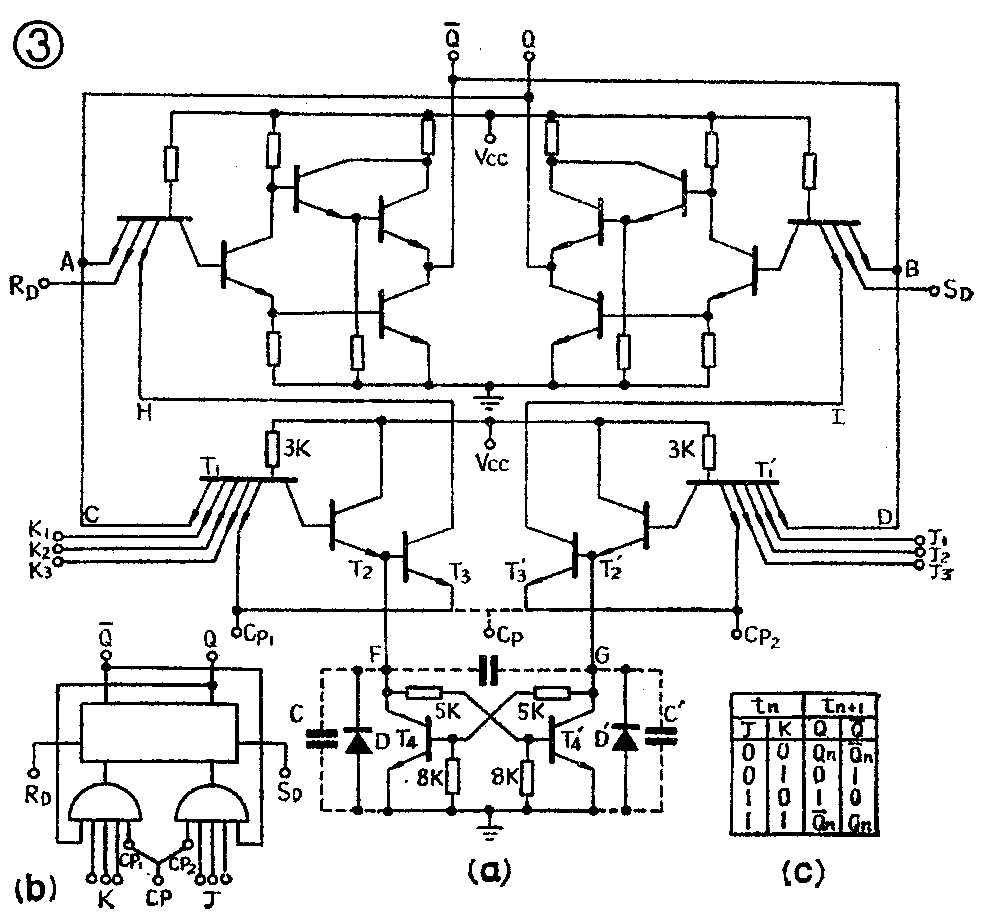

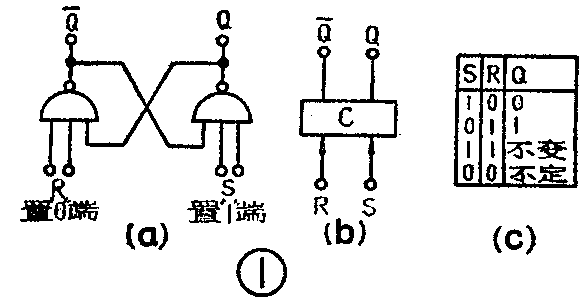

用RS触发器加上由电阻、电容组成的引导部分(图2),可组成最简单的计数触发器,但这种线路对元件要求很严格,引导不可靠,不合实用。目前广泛采用的是JK触发器和D触发器,图3是7CS23型JK触发器及其真值表,它由上下两部分组成,上半部跟RS触发器相似,称为从触发器;下半部代替RS触发器中的电阻电容,起引导作用,叫引导门(也叫计数头),形成主触发器。上下合起来成为JK主从触发器。

JK触发器除具备双稳态触发器具有的共性外,还有它的特性。我们先从它外部表现出的性能来看:

J、K多脚,组成与门;

J、K全高,分频计数;

J、K全低,入后不变;

J“0”K“1”,入后出“0”;

J“1”K“0”,入后出“1”。

它们的意思是:

(1)J控制端由三只脚J\(_{1}\)、J2、J\(_{3}\)组成与门;K控制端由三只脚K1、K\(_{2}\)、K3组成与门。

(2)J、K各端全部悬空或接高电平,从信号输入端CP输入计数脉冲,就成为计数触发器,起二分频作用。

(3)当J=K=“0”时,输入触发信号以后,输出保持原状不变。

(4)当J=“0”而K=“1”时,输入触发信号以后,输出为“0”,即Q=“0”、Q-=“1”。

(5)当J=“1”而K=“0”时,输入触发信号以后,输出为“1”,即Q=“1”、Q-=“0”。

R\(_{D}\)、SD端的作用,仍如前所述(这里加了附标D说明是直接置“0”、置“1”,以有别于令J=“0”或K=“0”通过CP置“0”、置“1”)。所以(2)至(5)四种情况下,R\(_{D}\)、SD端必须处于悬空状态或接高电平。

R\(_{D}\)、SD端与J、K端的功能不同:R\(_{D}\)端碰一下“0”电平,Q就立即为“0”;而J=“0”时,只是为Q=“0”作好了准备,必须在保持J=“0”的情况下,等待触发脉冲输入后,Q才为“0”。在J=“0”时,不论输入多少触发脉冲,Q总是“0”,不会再翻转。SD端和K端对置“1”而言,具有与R\(_{D}\)、J相似的性能。

JK触发器具有的这些特性和功能是由其内部结构决定的。让我们从连成最简单的计数触发器的情况来分析。这时J、K、R\(_{D}\)、SD全部悬空为“1”态,CP\(_{1}\)和CP2连在一起输入触发信号,并假定触发器的起始状态为“1”,即 Q=“1”,Q=“0”。则图3a左边A、C点电位V\(_{A}\)和VC为“1”,右边B、D点电位V\(_{B}\)、VD为“0”。V\(_{D}\)既为低电位,T1饱和,T\(_{1}\)′的集电极电流对T2′来说,恰好是一个反向基流,因而T\(_{2}\)′反偏而截止。在CP尚未输入信号时,T3′显然也截止,G点为低电位,故T\(_{4}\)基极也是低电位,T4也截止。当CP=“0”时,左边T\(_{1}\)管也饱和,同样道理,T2、T\(_{3}\)、T4′都截止。

当正脉冲到来后,左边T\(_{1}\)的全部输入端C、K、CP1全为“1”,右边T\(_{1}\)′的几个输入端中D仍为“0”,两边就发生了差异。T2′、T\(_{3}\)′和T4仍同原先一样截止,而T\(_{1}\)因全部发射结反偏,电流只能从+VCC经3K电阻流入T\(_{1}\)集电结,从而向T2提供正向基流,使T\(_{2}\)通导。F点变成高电位经5K、8K电阻分压使T4′基极电位升高,于是T\(_{4}\)′通导,G点变成低电位,T2工作在射极跟随器状态,输出阻抗很低,使电容C很快充电,最后形成V\(_{F}\)=“1”,VG=“0”,即T\(_{3}\)基极为高电位,T3′基极为低电位。可是因为CP\(_{1}\)=CP2=“1”,T\(_{3}\)和T3′的发射极电位高,所以T\(_{3}\)、T3′仍然都截止。当触发信号的后沿到来时,负阶跃使T\(_{3}\)发射结正偏而饱和,T3′则因基极为低电位而仍处于截止状态,致使二个集电极电位分别为V\(_{H}\)=“0”,V1=“1”。它们分别连在上部RS触发器的输入端,故使RS从触发器翻转:Q=“0”、Q-=“1”。

外触发脉冲解除以后,CP端为“0”,电容C上的电荷经饱和管T\(_{3}\)的发射结泄放,F点电位随之下降,T3基极电位降低,直至T\(_{3}\)截止,T4′也截止。到这时,T\(_{2}\)、T3、T\(_{4}\)′和T2′、T\(_{3}\)′、T4均截止,只是触发器状态已变, Q=“0”、Q-=“1”,V\(_{A}\)、VC变为低电位,V\(_{B}\)、VD变为高电位。这就为下一个触发脉冲信号使电路再翻转回去作好了准备(电容C、C′是由极间电容和寄生电容形成的)。

当J=“0”、K=“1”时(设这时触发器的状态为“1”),右边的T\(_{1}\)′发射结始终通导,T2′、T\(_{3}\)′截止。只有当CP=“1”时,左边的T1全部输入为“1”,T\(_{2}\)、T3才有可能通导。所以主触发器的两个输出端H和I,只有V\(_{H}\)在触发脉冲后沿到来时才会成为低电位,使从触发器变成Q-=“1”、Q=“0”,而VI始终为高电位。触发脉冲再来时,因Q=“0”、J=“0”,触发器维持原状不会再翻转。

同样道理,当J=“1”、K=“0”时,V\(_{H}\)始终为高电位,只有VI当触发脉冲后沿到来时,才会成为低电位。使从触发器呈Q=“1”、Q-=“0”状态。

7CS23型JK触发器的使用条件仍然受到一定限制,如触发脉冲的宽度不能太小,太小了不能把电容充电到足够高的电位,T\(_{3}\)或T3′就不能通导。触发脉冲的下降沿还必须很陡,如果下降速度慢,以致比电容的放电速度还慢,则T\(_{3}\)或T3′的基极电位总是小于发射极电位,T\(_{3}\)或T3′就不能通导。为了消除这个缺点,就要加大电容,譬如外接二极管D及D′(利用二极管极间电容)或在F点与G点间外接电容器。电容加大引起了新的矛盾,工作速度受到限制。

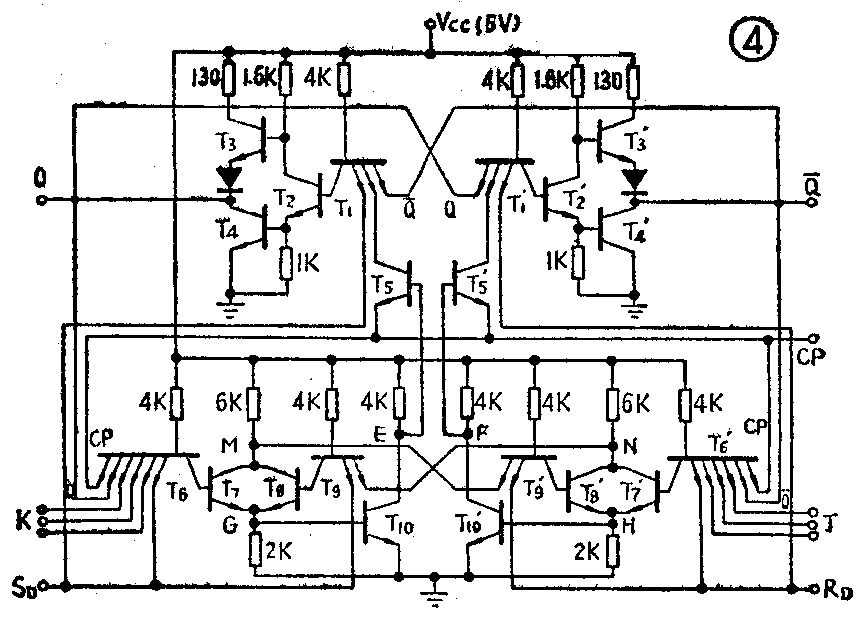

7CS43型JK触发器是一种性能较好的TTL型JK触发器(图4)。它的从触发器部分和7CS23型相似,中间部分T\(_{5}\)和T5′的作用也和图3a中的T\(_{3}\)和T3′相似,它的不同点主要在主触发器部分。从图4中看出,主触发器部分左右对称,各由一组“与或非”门组成,T\(_{6}\)、T9是多发射极管,分别组成“与”逻辑,这两组“与”门由”或”电路T\(_{7}\)、T8连接起来,T\(_{1}\)0是反相器。这样的电路结构不再需要电容器。

下部主触发器是怎样工作的呢?还是让我们结合计数触发器的作用来分析。设J、K、S\(_{D}\)、RD都悬空,且触发器起始状态为“1”;即Q=“1”、Q-=“0”。

当触发脉冲前沿到达后,CP=“1”,T\(_{5}\)、T5′因射极为高电位而截止,使上下两部分隔离。这时左边T\(_{6}\)管的全部输入为“1”,发射结反偏,集电极电流提供T7正向基流,使T\(_{7}\)通导,在T7射极的2K电阻上产生压降,使T\(_{1}\)0基极加上正电压,T10通导,造成V=“0”。而右边T\(_{6}\)′的输入端中与Q相连的那端为“0”,T6′的发射结通导,对T\(_{7}\)′形成反向基流,T7′截止,T\(_{1}\)0′基极电位为0,T10′截止,V\(_{F}\)=“1”。于是导致T5、T\(_{5}\)′基极电压的差异。

当T\(_{7}\)通导时,M点为低电位,使与之相连的T9′发射结通导,T\(_{9}\)′的集电极电流形成T8′的反向基流,使T\(_{8}\)′截止。既然T8′和T\(_{7}\)′都截止,N点便为高电位。这使与之相连的T9发射结反偏,T\(_{9}\)的集电结正向通导,形成T8的正向基流,保证T\(_{8}\)通导,M点为低电位。可见T8、T\(_{9}\)和T8′、T\(_{9}\)′互相制约,共处于一个统一体中,以保证M、N两点电位总是相反,也就保证了E、F两点的电位相反。和图3a中的T4和T\(_{4}\)′的作用相似,不过这里不再利用结电容和外接电容的充放电,改进了由于电容充放电带来的一些限制。

当触发脉冲后沿到来时,CP=“0”,T\(_{5}\)、T5′射极电位为“0”,这时因V\(_{E}\)=“0”而VF=“1”,使T\(_{5}\)截止而T5′通导,从而引起从触发器翻转,使Q=“0”、Q-=“1”,触发器状态呈“0”态。

当J=“0”、K=“1”和J=“1”、K=“0”时的情况也与7CS23型相似。

在置“0”和置“1”时,T\(_{8}\)、T9和T\(_{8}\)′、T9′的作用也很显著。以置“0”为例:因为R\(_{D}\)一方面连到上部T1′的一个输入端,另一方面连到下部T\(_{6}\)′和T9′的输入端,因此能同时改变主从触发器的状态。当R\(_{D}\)=“0”时,使T1′的一个输入端为“0”,迫使Q-=“1”,同时使T\(_{6}\)′、T9′的一个输入端为“0”,造成T\(_{7}\)′、T8′都截止,N点为高电位,H点为低电位,最后促使F点为高电位,E点为低电位。这时输入触发脉冲,只有T\(_{5}\)′有通导的可能,T5只能是截止,这就从整个触发器的内部保证了置“0”作用。

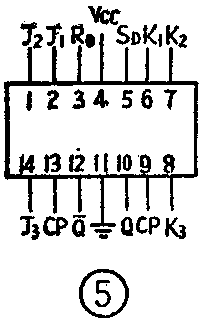

7CS23和7CS43型JK触发器的引线排列如图5。

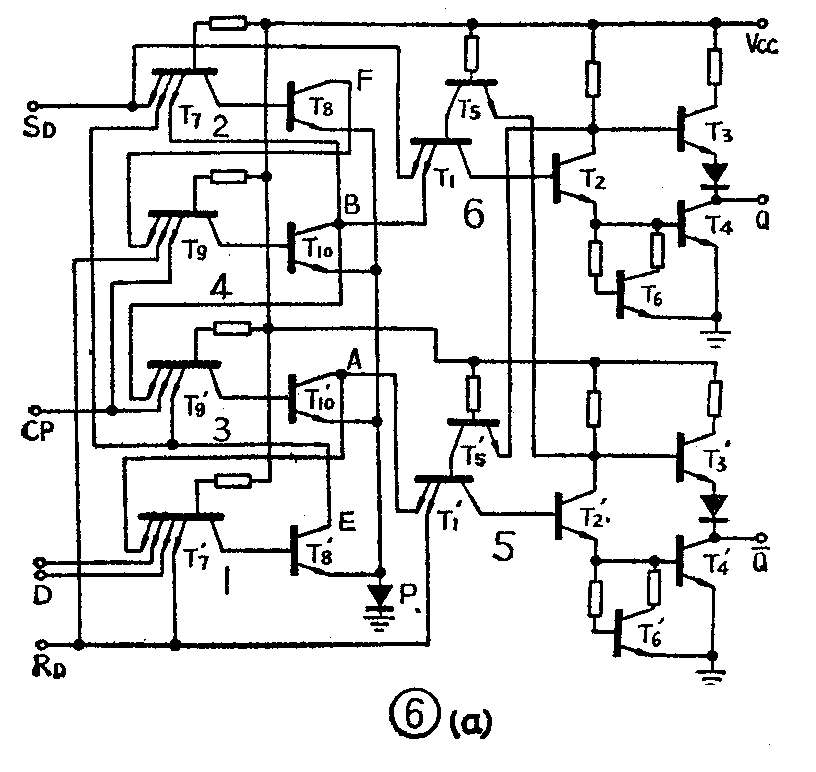

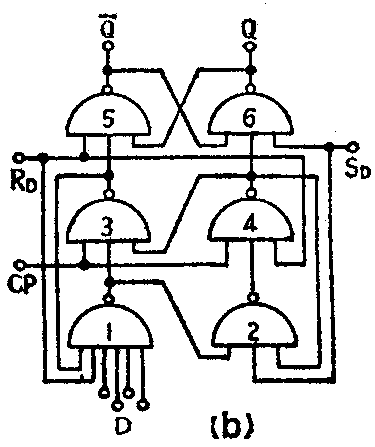

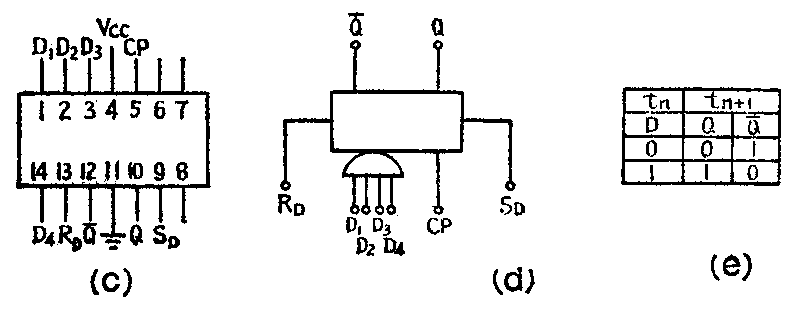

D触发器也是一种使用方便、功能完善的触发器。其特点是D输入端的信号,必须借助下一个触发脉冲。才存贮到Q中,所以也叫延迟触发器。具体地说,如图6a所示,当D=“0”时,必须等待触发脉冲到来以后,Q才呈“0”态;当D=“1”时,必须等待触发脉冲到来以后,Q才呈“1”态。图6e是D触发器的真值表。可见,D触发器的D端是决定触发器将成为何种状态的主导方面,外触发信号CP是通过D的状态起作用的。图6a是D触发器的内部线路图,整个D触发器由六只与非门电路组成,门5和门6组成RS触发器(与非门内部略有更动,是为了提高抗干扰能力、提高传输速度、改善转移特性和缩短内引线),决定触发器输出状态的,仍然是这一部分;门1、2、3、4为简易与非门电路,因为它们需要的负载能力很小,只要起到有效的控制作用就可以了。

设触发器的起始状态为“0”态;即 Q=“1”、Q-=“1”,且R\(_{D}\)、SD端悬空为高电平。

若D=“0”、CP=“0”。这时T\(_{9}\)和T9′的发射结正偏,T\(_{1}\)0、T10′截止,门3和门4的输出端A、B两点为高电位“1”。A、B两端连到RS触发器T\(_{1}\)′、T1的发射极,起控制RS触发器翻转的作用。对门1来说,因D=“0”,T\(_{8}\)′截止,输出端E为高电位“1”。对门2来说,全部输入(SD、E、B三端)都为“1”,T\(_{7}\)截止,T8因获得正向基流通导,输出端F为低电平“0”。由于F连到门4的T\(_{9}\)发射极,所以门4被封住,不论CP如何,T9总处在通导状态,T\(_{1}\)0截止,VB总为“1”。而门3T\(_{9}\)′的发射极中只有连CP的一端为“0”,其余都为“1”,所以处于准备接收输入脉冲的状态。这时当第一个CP脉冲的前沿到来时(D=“0”而CP=“1”),门3因输入全部为“1”使输出VA为“0”,即对RS触发器发出置“0”脉冲,使Q-保持为“1”。同时因A又连到T\(_{7}\)′的一个发射极,而将门1封住,所以,如果下一个触发脉冲没有到来的话,D端电平的任何变化都不改变触发器的状态。

若D=“1”,CP=“0”。同样道理,A、B两端仍为高电平“1”。但这时门1因输入全高而使输出端E为低电平“0”,E连到门3和门2的输入端,因而封住门3和门2,不论CP状态如何,门3输出V\(_{A}\)、门2输出VF都为“1”,而F又和门4的输入端相连,致使门4输入端除与CP相连的那一端外,其余各端均为“1”,处于准备接受CP脉冲的状态。当CP=“1”时(D=“1”),门4因输入全为“1”而输出为“0”,于是使RS触发器翻转为Q=“1”。这相当于把D中的“1”信号存贮到Q中去了。与此同时,门4输出端V\(_{B}\)为“0”,使与之相连的门3封住,D端电平的任何变化不会影响门3的状态,也就不会影响到触发器的状态,除非再输入触发信号。图6b是D触发器的逻辑图,读者可以根据它自行分析D触发器的工作情况。图6c是D触发器的引线排列图。

将D触发器和JK触发器从形式上比较一下:门5、门6组成RS触发器,如同JK触发器的从触发器;T\(_{1}\)0和T10′如同JK触发器中起引导作用的晶体管,控制从触发器的状态;门1、门2、门3、门4如同JK触发器里主触发器的作用;R\(_{D}\)和SD的作用和JK触发器的相同。

使用JK触发器和D触发器时应了解的基本性能,可以对照第二篇门电路来理解。这里只讲一下关系到用多级触发器组成计数器时搭配问题的三项性能:电压传输特性、输出低电平和输出电流的关系、输出高电平和输出电流的关系。

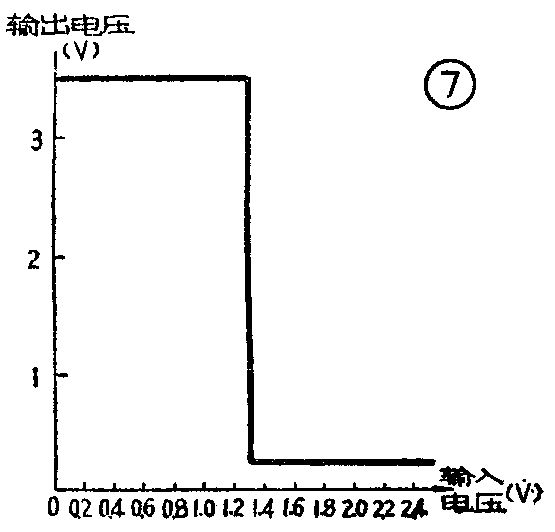

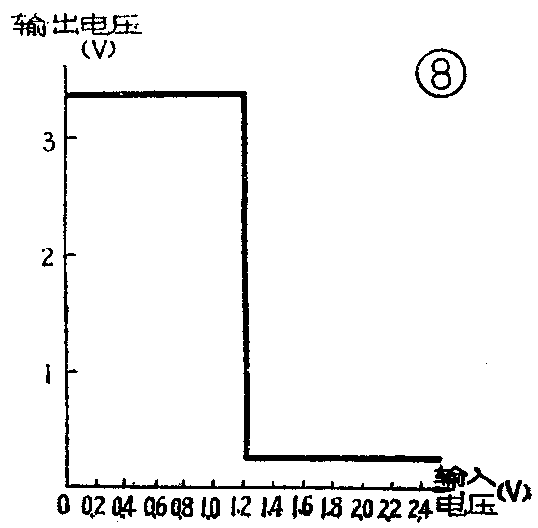

图7是7CS43型JK触发器电压传输特性曲线,图8是7CY13型D触发器的电压传输特性曲线,和门电路的电压传输特性曲线相比,触发器的传输特性曲线转换时,下降沿很陡直。

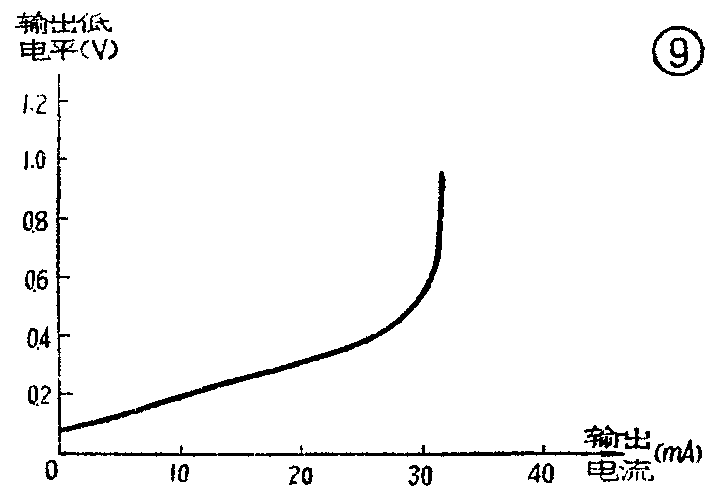

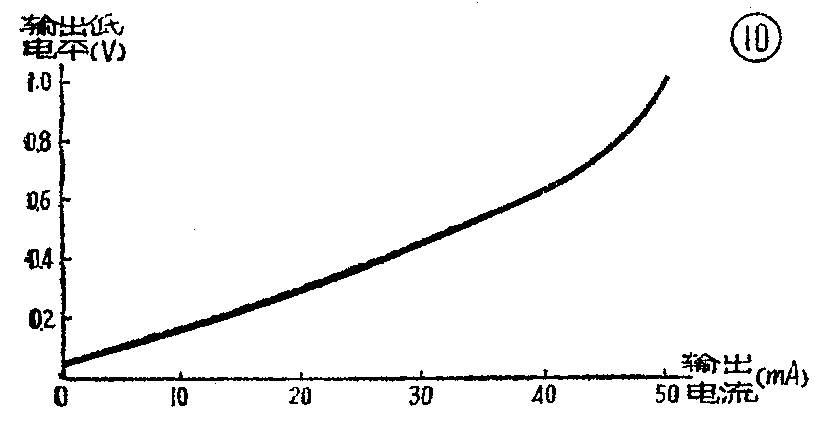

图9是7CS43型的输出低电平随输出电流变化曲线(图10是7CY13型的)。当输出端带的负载较重,电流增大时,输出低电平上升,到一定程度,输出电流再继续增大时,输出低电平急剧升高,不能正常工作。这说明输出晶体管在其注入基流不变的情况下,由于外负载注入电流太大而脱离饱和状态进入线性区。

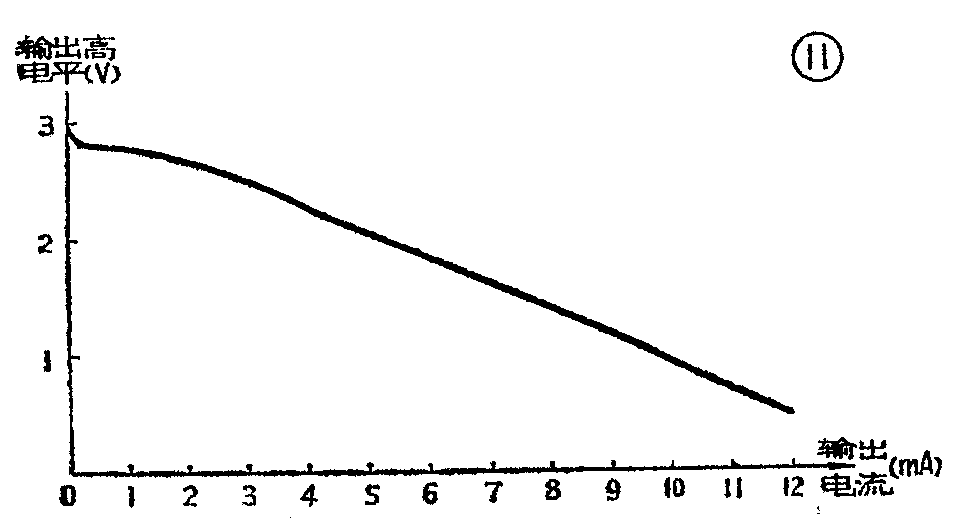

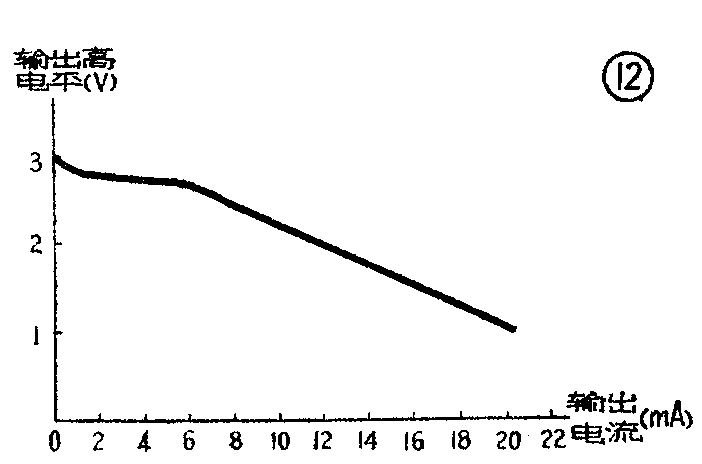

图11是7CS43型的输出高电平随输出电流变化曲线(图12是7CY13型的)。当输出端带的负载较重,电流增大时,输出高电平下降,输出电流增大到一定程度时,输出高电平将因下降过多而不能正常工作。

关于工作频率问题,JK触发器和D触发器可以达到几兆赫至几十兆赫,对于一般应用已经足够了。(天津市四十二中学 凌肇元)