半导体集成电路(以下简称集成电路)是六十年代发展起来的一门电子电路微小型化新技术。由于集成电路有许多优点:重量轻、体积小、使用方便可靠、适于大规模自动化生产等,十几年来其产量、质量都获得了很快的发展。目前,集成电路已被广泛用于宇宙航行、导弹、电子计算机、程序控制系统以及通信、广播、电视等许多方面,北京大学等单位共同研制成功的百万次集成电路电子计算机就是一个例子。

显微镜下看集成电路

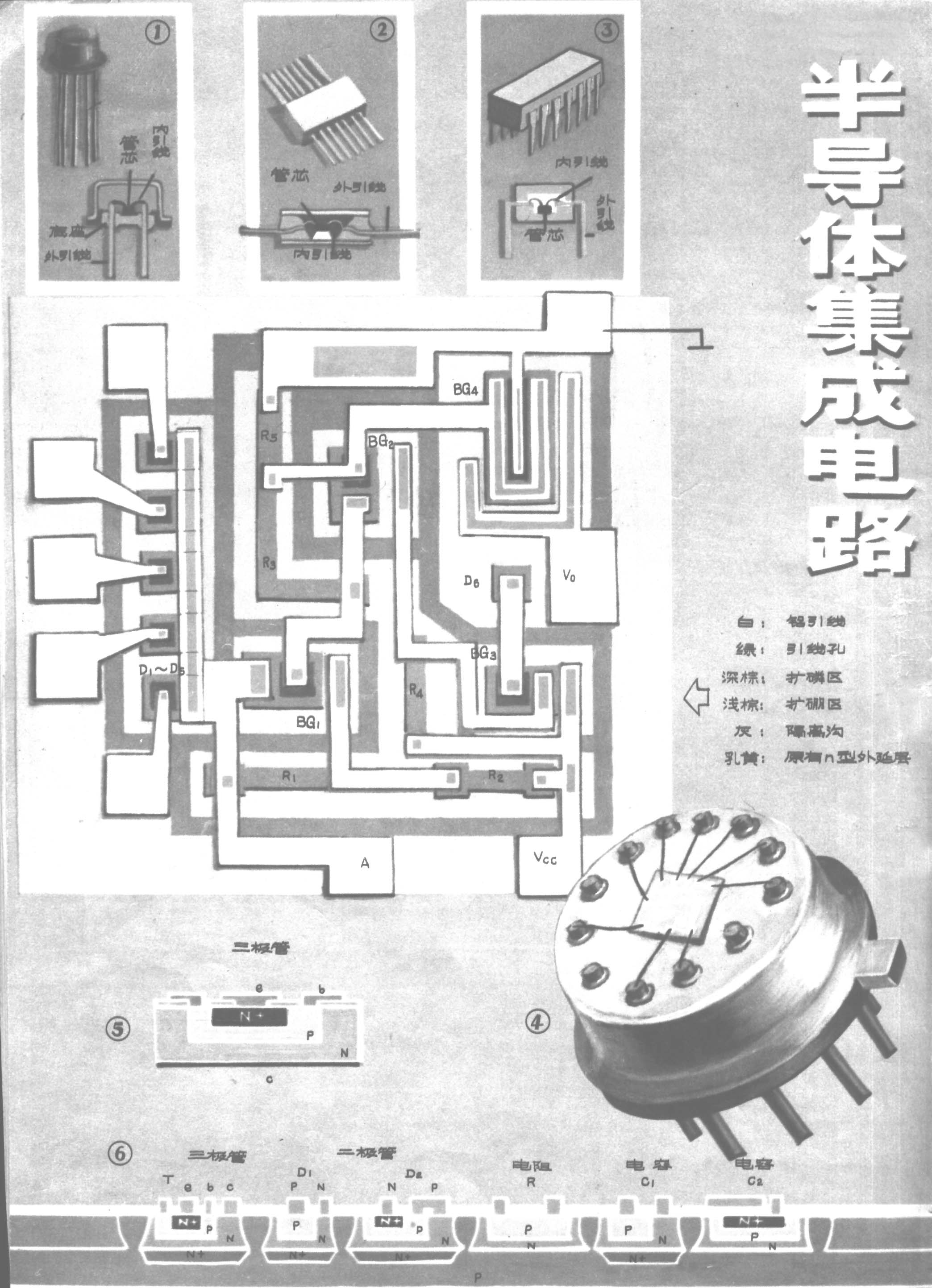

集成电路的外表主要有三类(封底图1、2、3):圆型、扁平型和双列直插型。圆型用金属外壳,其它两类用陶瓷外壳或用塑料铸成。如果打开外壳(封底图4),其核心都是一片单晶硅片(也有几片的),有许多细金属丝把它与管座上的管腿连结起来。在这小小的硅片上制作了一个完整的电路(如放大电路、振荡电路、开关电路等)。在显微镜下可以看见硅片上那密密麻麻的银白色的铝引线和这些引线所连接的许多电路元件,即电阻、电容器、二极管、三极管等。这些元件的样子与我们日常见到的同类元件的样子大不相同(见封底图片)。在较简单的集成电路里,大约有十来个元件,而复杂的集成电路里甚至可以制作上万个元件。人们常用“细如发丝”来形容物体之细,但集成电路里的铝引线只有头发丝粗细的几十分之一;人们又常用“芝麻大的地方”来比喻地域之窄,殊不知正是在这芝麻大的地方却制作了成百个电路元件和它们的连线。这小小的管芯,从备片到制成,需要经过四、五十道工序。

集成电路的制作过程

半导体集成电路目前共分两类。一类是在普通NPN硅平面晶体管工艺基础上发展起来的双极型集成电路;另一类是在MOS(即金属——氧化物——半导体)型场效应晶体管工艺基础上发展起来的MOS型集成电路。本文仅简单地介绍一下双极型集成电路的制作过程。

当我们制作一个电路,比如一个半导体收音机电路时,实际工艺是分成两步的:首先将电路所需的元件——电阻、电容器、电感、三极管、二极管等——制作出来(当然这一步早由元件厂为我们做了),其次再将元件连接成电路。这后一步还可细分为把元件固定在绝缘板上、焊接元件间的连线以做成线路板、在线路板上接出输入(接磁性天线)、输出(接扬声器)、电源、地线等引出线这样一些小的步骤。

集成电路的工艺既然是制作一个整体电路,当然也包括这样两个步骤。只是制作元件和连接成电路所采用的方法不同。半导体集成电路为实现这两个步骤,采用了“平面工艺”技术。其工艺并没有超出制作外延硅平面三极管所采用的外延、氧化、光刻、扩散、蒸发等工艺的范围。集成电路的制作像硅平面三极管一样要有硅片准备、管芯制作这样一些步骤,又像焊电路时一样必须实现电路连接,并接出必要的输入,输出、电源、地线等引出线以便与外电路连接。

集成电路的制作与硅平面三极管的制作有许多相似之处,所以下面我们首先介绍一下硅外延平面三极管的制作方法。

硅外延平面三极管的制作

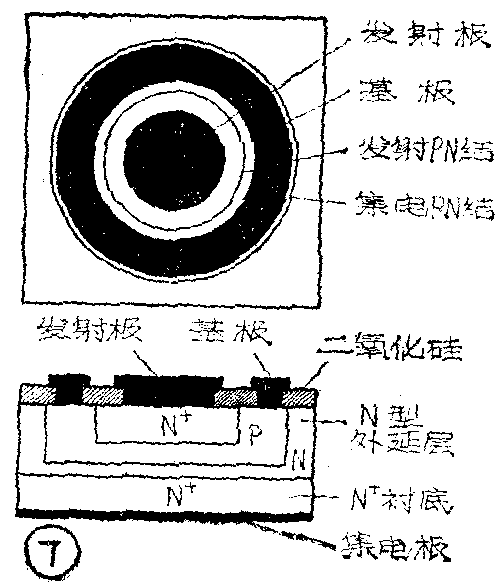

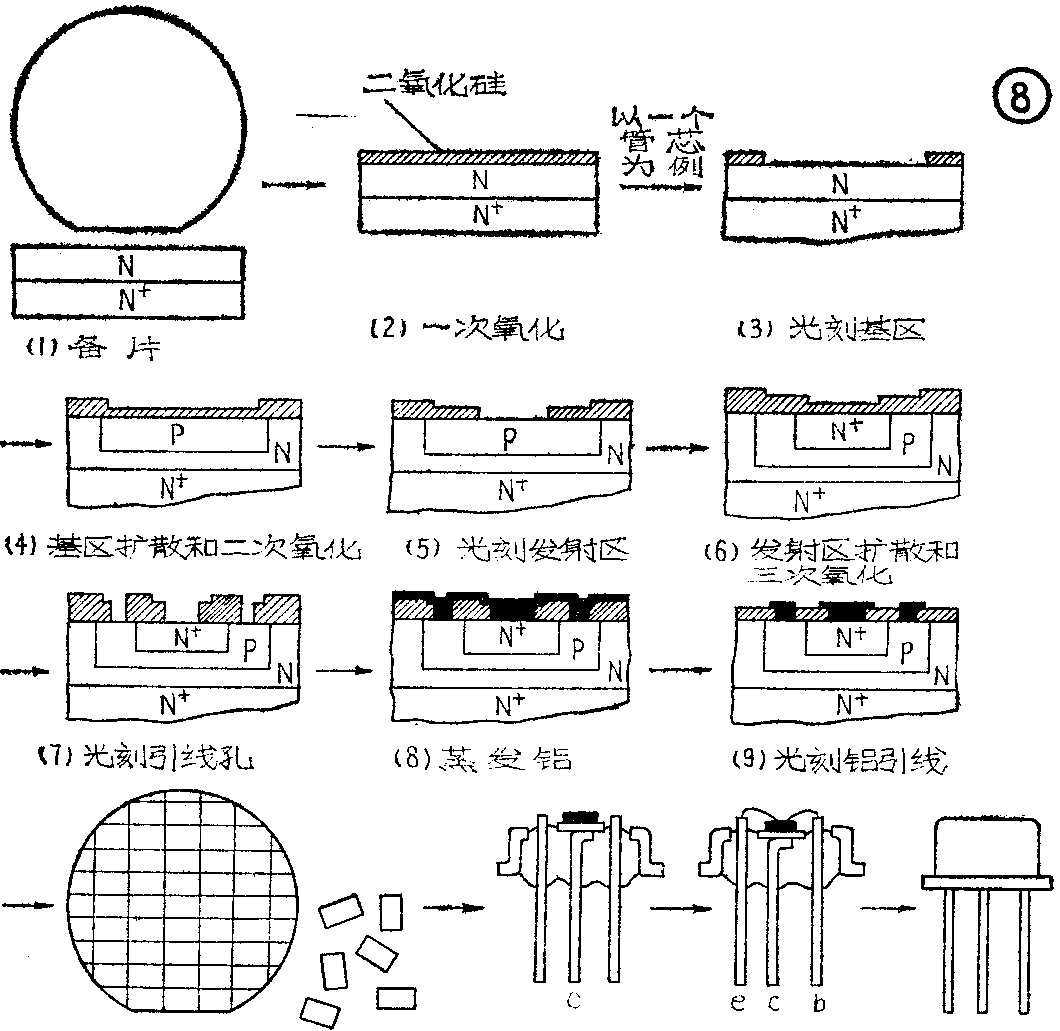

硅外延平面三极管的管芯顶视和剖视图见图7。我们知道,杂质硼、铟等掺入半导体可使半导体变成P型,而杂质磷、锑等掺入半导体可使半导体变成N型。因此我们如果取N型硅片为集电区,使其上一个局部区域掺上硼变成P型,作为基区,再在此基区中的一个局部区域掺上磷,重又变成N区作为发射区,则可做成一个NPN的三极管。工艺上通过所谓定域扩散的办法实现上述设想。在高温下(1000℃以上)硼和磷都能以较快的速度向硅中扩散,但同样温度下它们几乎不能向二氧化硅中扩散。因此,如果我们先将硅片用二氧化硅覆盖起来,然后将此氧化层中指定部位内的二氧和硅去掉,露出硅来进行扩散,则去掉了二氧化硅的地方(叫“氧化层窗口”)有杂质扩入,其余部分由于氧化层的掩蔽,不受杂质影响。这就叫定域扩散。为了按指定部位开氧化层窗口,必须用到光刻技术。硅平面管工艺正是通过对硅片反复使用氧化——光刻氧化层窗口——定域扩散这样的工艺循环来制作三极管的。具体工艺流程如图8所示。

⑴ 硅片准备:用低阻N\(^{+}\)型硅单晶按一定的晶体方向切成薄片、用金刚砂磨去切片刀痕、再经镜面抛光。然后用外延生长技术生长一层掺杂较低的N型外延层(具体掺杂多少由所作管子特性要求决定)。管芯就制作在此外延层上。

⑵ 一次氧化:片子经清洗后放入高温炉的石英管内,送入氧气,在高温下生成一层薄的二氧化硅层。

⑶ 光刻基区:按照预先制好的基区掩模版用光刻腐蚀的办法刻蚀出基区氧化层窗口。

⑷ 基区扩散和二次氧化:将硅片放入高温炉内,通入含有杂质硼的气流,硼的分子在开有“窗口”的地方扩入硅片,将“窗口”内的硅由N型变成P型,形成基区——集电区PN结。随即通入一部分氧气,使基区上方生成氧化层,将“窗口”再次掩蔽起来。

⑸ 光刻发射区:用发射区掩模版在基区内刻出发射区窗口。

⑹ 发射区扩散和三次氧化:将硅片放入高温炉内含有杂质磷的气流里,磷扩入发射区“窗口”,将发射区内的硅又由P型变成N型,形成NPN三极管。同时进行三次氧化将“发射区窗口”掩蔽起来。

⑺ 光刻引线孔:经过三次氧化后的硅片表面覆盖着一层绝缘的二氧化硅层,为了引出基区、发射区的引出线,必须再次使用光刻的办法刻出基区和发射区的引线孔窗口。

⑻ 蒸发铝:在高真空条件下使铝熔化,铝分子因蒸发(如同水蒸发为蒸汽那样)而飞离液态铝表面,淀积于硅片表面上,形成一层一到几微米的薄铝层。这层铝通过“引线孔窗口”与硅的基区、发射区接触,其余部分与硅体绝缘。

⑼ 光刻铝引线:除了两个电极引线部分外,将其余部分的铝通通用光刻办法腐蚀掉。同时基区铝引线和发射区铝引线也彼此分开了。

⑽ 管芯分割:通常在一块硅片上同时制作着几百,几千个管芯。本工序内用激光或金刚刀将其一个个分割开来。

⑾ 烧结:将管芯烧结在底座上。底座与管子的集电极管腿是连在一起的,因此从管芯下方出来的集电极通过烧结直接与C管腿连接。

⑿ 内引线焊接:将管芯上的基区、发射区铝引线分别与管座上的相应管腿用金丝或硅铝丝焊接起来。

⒀ 封帽:此外,管子还要经过老化筛选、涂漆、测试分类、打印、包装等工序。

集成电路的工艺特点

集成电路的制作和硅平面三极管的制作工艺相似。下面谈谈集成电路的几个特殊的工艺:

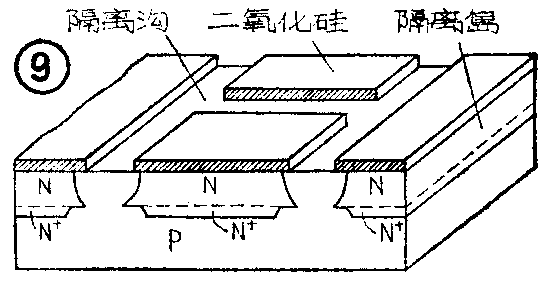

(一)隔离:集成电路的各元件不是固定在绝缘板上而是制作在一块硅片上,因此必需采取措施使这些元件之间处于电学上彼此绝缘的状态,因而带来了集成电路制作中特有的“隔离”工艺。工艺上不是先做好元件再使其隔离的,而是先使硅片划分成许多彼此隔离的区域,再在此区域内制作元件,最后连成电路。划分隔离区的工序叫“隔离”,隔离开来的区域叫“隔离岛”,“隔离岛”之间的绝缘层叫“隔离沟”。元件制作在隔离岛上(图9)

隔离有多种办法。常用的有利用二氧化硅绝缘特性制作的“介质隔离”和利用反向PN结的高阻特性制作的“PN结隔离”。我们以PN结隔离为例介绍一下隔离的原理和方法。

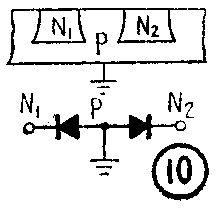

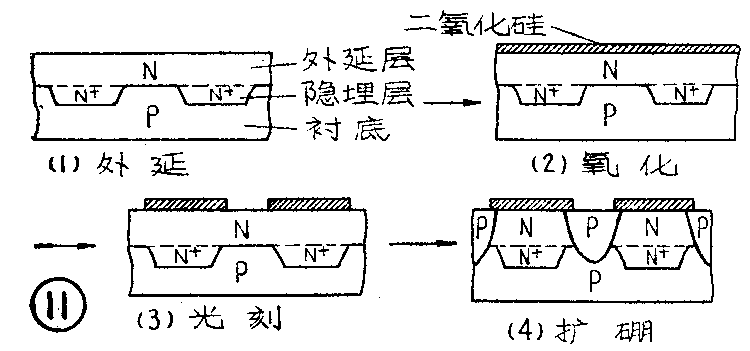

大家知道:反向偏置的PN结具有高阻抗。如果我们象图10那样,在每个必须隔离的元件之间制作两个“背对背”的PN结,在使用时又使基片P区接于电路最低电位上,则两个PN结均为反向偏置,即处于高阻状态,从而达到隔离的目的。隔离的工艺见图11:

①取已制作了N\(^{+}\)型低阻隐埋层的P型硅片,去氧化层。外延生长一层N型外延层;

②在硅片表面生长氧化层;

③按隔离沟掩模上的图形刻去沟内氧化层;

④扩硼。将整个外延N型区扩穿,使与下方的衬底P区连接。这样,N型区就成了被P型区从四面和下方隔开的“孤岛”了。

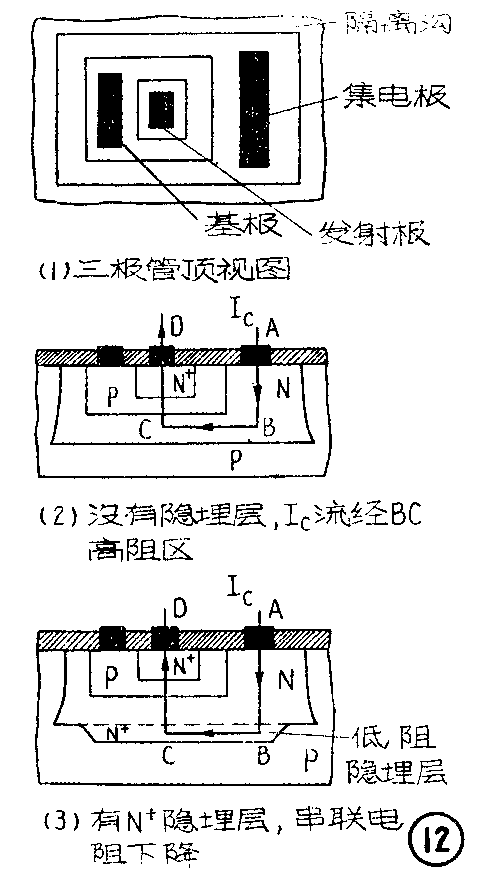

(二)隐理层和三极管的制作:集成电路里的三极管都制作在隔离岛上,而且其三个电极都要通过金属引线与其它元件连接,所以它的集电极引线也要从硅片表面引出(图12(1))。这样,如图12(2)所示,集电极电流I\(_{c}\)是沿着ABCD的方向流过三极管的。其中BC段是只有几微米宽的横向通道,电阻很大。这样大的串联电阻必然引起管压降的上升,开关特性、频率特性变坏等。因此,在外延之前先在原始P型硅片上制作N\(^{+}\)型低阻隐埋层(图12(3)),使Ic避开了那一段高阻通道的影响。具体工艺也是利用氧化——光刻——定域扩散的办法。所用N型杂质是锑。

在“隔离”工序以后的三极管制作就完全与上一节介绍的单个硅平面管工艺相同了。

*通常总是用N(或P)旁附标以“+”号表示高掺杂的N(或P)型区,即N\(^{+}\)(或P+)区。其特点是电阻率很低。也称强N区(或强P区)。有时也用N\(^{-}\)(或P-)表示弱N型或弱P型,但没有定量的明确分界。

(三)二极管的制作:集成电路里的二极管有两种做法:其一是象制作三极管一样,但在做过基区硼扩散和二次氧化后不再刻出发射区,直到刻引线孔时才将基区引线孔和原隔离岛上的N型集电区引线孔刻出来,利用硼扩散形成的PN结构成二极管(封底图6中D\(_{1}\));另一做法是因集成电路里三极管的制作并不比二极管制作困难,可以在制成三极管后在布线互连时将三极管的三个电极以适当方式连接起来构成二极管。封底图6中D2就是将三极管的基区和集电区短路利用发射PN结构成的二极管。

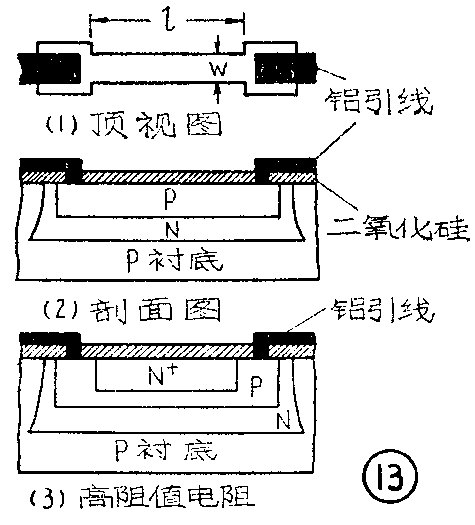

(四)电阻:集成电路里的电阻通常都是利用半导体的扩散层电阻制成。我们知道,半导体的电阻率是与掺杂浓度有关的。在集成电路生产中,基区扩散层掺杂浓度较低,一般用于制作阻值大的电阻(图13(1)、(2))(例如50欧姆~500千欧姆的范围较易做到)。而几欧姆的低阻值电阻可以用掺杂浓度高得多的磷扩散层做。此外还可以象图13(3)那样利用发射结下方的窄而且掺杂浓度很低的弱P型区制作高阻值电阻。但其阻值很不容易控制,误差较大。另外也有用在氧化层外蒸发或溅射镍铬的办法制作电阻的。图13(1)、(2)所示为硼扩散电阻。显然l愈长和W愈窄电阻值愈大。

(五)电容器:利用平面技术难以制得大容量的电容器。小容量电容器通常有两种办法获得。

一种办法是利用PN结电容。PN结反向偏置时相当于一个电容器。可以和三极管同时制得(封底图6C\(_{1}\))。PN结电容的大小和结面积、结两边掺杂大小以及结上反向电压的高低有关。通常总是通过控制结面积制得不同容量的电容器。可以利用发射PN结或集电PN结或二者的并联制得电容器。

第二种办法是相当于作成一个平行板电容器,其极板是铝电极和硅层本身,例如象封底图6C\(_{2}\)那样利用掺磷N\(^{+}\)区,介质是二氧化硅层。

(六)互连:工艺上类似于印刷线路板的制作。只不过这里构成连线的不是铜而是蒸发于硅片上的铝,这层铝如前述仅在刻有引线孔的地方与N或P型硅相连。

(七)后工序:互连以后就进行管芯分割、装架烧结、内引线焊接、封帽、老化筛选、涂漆、打印、包装等后工序了。在内引线焊接时,由于还要接通电路的输入、输出、电源、地线等,因此内引线和管腿数目都要多一些。

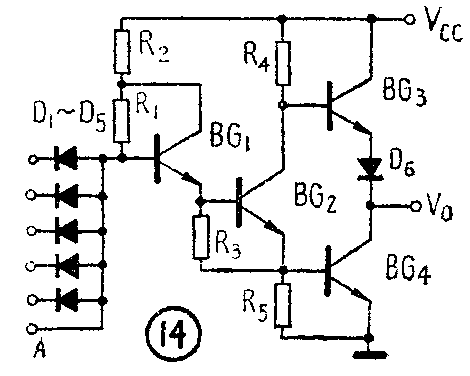

在封底中部给出的是一个DTL与非驱动器电路管芯的示意图。其具体线路图见图14。

一、“一次氧化”:片子经清洗后送入高温炉的石英管内(1200℃左右),管内通有氧气。经过一段时间后(30~60分钟)硅片表面生成了一层薄薄的二氧化硅层。

二、“基区扩散和二次氧化”:这一步在实际生产中常分成预扩散和主扩散两步。首先将硅片推入940℃左右的预扩炉石英管内,管内通有含硼氮气,硼分子通过基区“窗口”预淀积于硅片表面,但由于炉温较低,硼分子尚不能深入硅体内部,因此再将硅片推到1200℃左右的氧化炉石英管内,管内预先通有氧气,这样,在硅片表面生成一层氧化层的同时,预淀积于硅片表面的硼杂质又进一步深入扩散到硅片里,形成所需的PN结。而新生长的氧化层又掩蔽了基区“窗口”。(吴思齐)