透视Intel的65nm生产技术

技术大讲堂

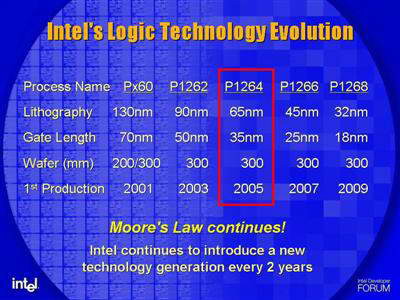

领先世界的半导体生产技术一直都是英特尔一切优势的基础,理所当然,英特尔不但把利于制造作为一切思考的出发点,在半导体生产设备上的大手笔投资更是令人瞠目结舌。在2005年IDF上,英特尔正式公布代号为P1264的65nm生产技术,更先进的半导体制造技术将大大提高CPU性能和降低生产成本,让英特尔在与同行的竞争中处于更加有利的地位。

一、为什么需要65nm生产技术?

处理器生产技术的进步主要体现在蚀刻尺寸的不断缩小、各个硅晶体管连接导线的宽度不断缩小之上。那么,生产技术的改进究竟可以带来多少实质性的好处呢?

1.更高的芯片集成度

更先进的生产技术最直接的好处就是可以让芯片的集成度大大增加。我们知道,为了获得更高的性能,芯片内容纳的晶体管数会变得越来越多。对CPU而言,便是运算核心的增强和缓存单元的增大。现在的Prescott核心的Intel CPU,晶体管总数达到1.25亿个,而下一代的Yonah双核心处理器晶体管规模将突破3亿个。同时为了尽可能提高性能,各厂商都热衷于增大CPU缓存容量。由于CPU的高速缓存要求运行在数GHz的高频率上,因此只能使用SRAM类型的存储单元。SRAM的每一个比特位需要占用6个晶体管,存储密度很低,1MB容量的二级缓存就需要占用5000万个晶体管,这是一个相当惊人的数字。而按照现有发展趋势,每隔两年CPU的二级缓存容量都会增大一倍。

那么厂商是如何在处理器那么狭小的空间内集成越来越多的晶体管呢?这时厂商就必须进一步缩小硅晶片内微细元件的尺寸以腾出空间来容纳增加的晶体管和元件。采用蚀刻尺寸更小的技术成为了厂商们必走之路。同时随着晶体管尺寸的缩小,每颗晶体管的单位成本也有所降低,而整体的微型化同时也缩小了晶体管门极尺寸。门极是晶体管中负责阻挡或让电流通过的开关,门极越窄,晶体管开启与关闭的速度越快,使用晶体管的线路因此得以提高工作速度。因此,处理器含有越多的晶体管,它们的速度就越快。

2.降低功耗才是根本原因

英特尔之所以如此迫切引入65nm生产技术,原因之一就是为了降低处理器的功耗。

我们都知道,Inter Prescott CPU最大的问题就是功耗过高,而罪魁祸首就是漏电流。所谓漏电流,是指晶体管不管导通还是截止(开关),均有电流流动。由于本来为截止的时候也有电流流动,因此就会造成电量的浪费。而在采用90nm工艺的Prescott中,漏电流造成的耗电量增加是非常严重的问题。另外,要想提高晶体管的开关切换速度,即工作频率,设计半导体时必须使电流在晶体管中易于流动。过去晶体管越小,开关所需的电压就越低,耗电量也就越小。而目前的情况是由此减少的这部分耗电量全部被漏电流抵消了。

当然,半导体制造商并非完全没有预料到泄漏电流的增加。但降低漏电流的技术在90nm工艺下没有达到实用水平,漏电流的增加量也超过了半导体制造商的预想。而减少漏电流通道等漏电流降低技术要等到65nm时代才能完全充分使用。

二、65nm制程的主要技术特性

从90nm工艺向65nm的转变过程中,引入各项先进技术是必然的事情。相较以往,英特尔的65nm生产技术有着诸多特色。

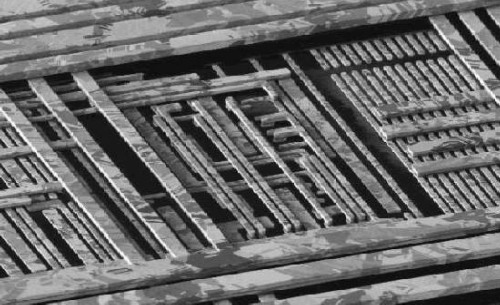

1.八层互连布线架构与高K值材料

与在Prescott核心上使用的90nm生产技术相比,英特尔的65nm生产技术最明显的改进是实现了8层互连布线结构。目前CPU中集成的晶体管数目已经数以亿计,厂商为了能在有限的CPU内核空间中集成更多的晶体管,往往使用一种三维的堆叠结构。因此实现了8层互连结构,每一块芯片可以容纳8个不同的逻辑电路层,容纳更多的晶体管。不过虽然实现8层互连布线结构可以容纳更多的晶体管,但同时也要面对更多的技术问题。最明显的问题就是电路层之间的线状电容效应及漏电流问题都会随着晶体管的增加而变得严重起来。

我们都知道,电容值与绝缘物的介电系数(K值)成正比,所以为了降低漏电流以及导线电流的线状电容效应,高K门极绝缘层以及低K导线绝缘层就成为半导体产业界的技术发展重点,尤其门极绝缘层技术已经被公认是65nm以下生产技术的关键。门极绝缘层就是在硅晶圆表面“长”一层薄薄的二氧化硅,其做法是将晶圆暴露在氧与水蒸气中,就某种意义来说,就是使硅“生锈”。但与钢板生锈的情况不同的是,此处的氧化物并不会粉碎脱落,它们反而紧紧附着在表面,因此如果要进一步氧化,氧原子必须扩散穿过这一层氧化物,才能抵达下面全新的硅。这个扩散规律提供给芯片制造商一个控制氧化层厚度的方法。举例来说,只要让氧进行短时间的扩散,就可以制造出目前微小晶体管门极绝缘所需的薄氧化层。问题是,现代芯片中的门极氧化层只有几个原子的厚度,已经薄到不容易放置在晶圆上的地步。对策之一当然是把它做得厚一点。不过麻烦的是,随着氧化层的厚度增加,门极电容的容量会跟着降低。如果门极的电容容量太低,通道中就没有足够的电荷来导电。解决之道就是用二氧化硅以外的材料来作为门极的绝缘体。

在65nm生产技术中,IBM和AMD仍用SOI(绝缘层上覆硅,Silicon On Insulator)来作为门极的绝缘体,SOI有效隔断了各电极向衬底流动的漏电流,使之只能够通过晶体管流动,但它对于同级晶体管之间的阻隔效果并不理想。英特尔早先认为SOI技术难度太大,所以决定另辟蹊径——采用高K值的氧化物材料来制造晶体管的栅极,英特尔称之为“高K门极电介质”(High K gate Dielectric)。这种材料对电子泄漏的阻隔效果可以达到二氧化硅的10000倍,电子泄漏基本被阻断,这样就可以在绝缘层厚度降低到0.1nm时还拥有良好的电子隔绝效果。正是采用了高K值材料,65nm生产技术虽然让门极宽度由50nm缩至35nm,但是门极绝缘层厚度依然保持1.2nm,英特尔压制漏电流的企图不言而喻。

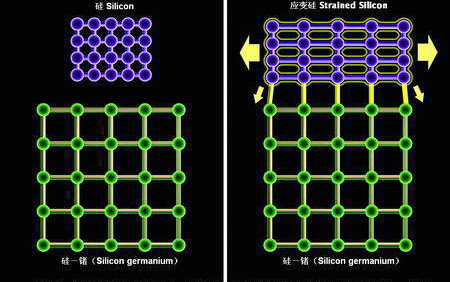

2.第二代应变硅技术

除了采用高K门极绝缘层以及Low-K导线绝缘层外,在65nm工艺中英特尔决定采用更先进的第二代高性能应变硅。应变硅是为了增加晶体管电流与电路切换速度的一种解决方案。科学家发现,如果强迫硅晶格稍做伸展(约1%),穿过晶体管间的电流速度会提高不少,建立在硅之上的晶体管因而得以操作得更快。需要注意的是,应变硅技术并未能解决晶体管门极微缩(scaling)的问题;当晶体管门极长度缩短,会使门限电压(threshold voltage)降低,进而产生“短通道效应”(short-channel effect),这时需要使用绝缘硅来控制这种效应的发生。令人感到遗憾的是,应变硅技术在Prescott中的表现并不是很令人满意,并不能有效降低电泄漏现象所带来的影响。不过,英特尔宣称在未来65nm生产技术中采用的第二代应变硅技术将要优于90nm工艺中的第一代应变硅技术。

事实上,英特尔的半导体生产技术发展一直都有着完善的布局,环环相扣,历代生产技术之间都有着相当密切的关连。Intel公司宣称,其第二代应变硅技术使得晶体管的性能提高了10%~15%,同时没有电流泄漏增加。缩小20%长度的门极,结合应变硅的效应,英特尔的65nm生产技术让逻辑门的交换频率可以达到90nm的1.4倍,换言之,处理器的频率就有上6GHz的可能。为了进一步降低漏电流,英特尔也在65nm中导入了NMOS Sleep Transistor技术,目前英特尔将它应用在动态关闭SRAM所用不到的区块,达到降低漏电流的效果。与90nm技术生产的晶体管相比,65nm技术在同样的性能情况下可以使电流泄漏减低80%。这样的话,65nm技术生产的处理器在没有增加电流泄漏的情况下,提高了性能。

3.更先进的Lithography(微影)技术

此外,微影生产技术在处理器制造中一直扮演着举足轻重的角色。随着处理器生产技术的不断发展,微影技术也需不断提高分辨率以制作更微小的线路。不过,自从采用130nm生产工艺后后,微影技术就已经处于落后的局面,理论上如果采用65nm生产工艺,目前一般的193nm微影波长是不能满足需要的。

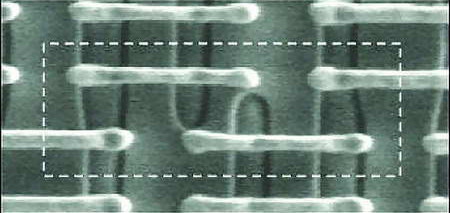

提示:微影技术是制造晶体管及它们之间的连结的关键技术,其主要是指利用一定波长的紫外线透过掩膜后照射在硅晶元上,将掩膜上的电路图像完整地复制到硅晶元上从而形成所需要的电路图形的过程。掩膜其实可以看作是CPU内核电路图的微缩“底片”,厂商事前先将一幅有着非常复杂的设计模型的原图缩小成极细微的蚀刻掩膜。未曝光的光阻剂经化学处理及烘烤而硬化,因此能保护阴影下的区域避过稍后的化学蚀刻。

由于早在2003年5月Intel就宣布不会将157nm微影设备引入到65nm生产技术中,将继续使用193nm微影技术。因此,根据65nm工艺的需要,英特尔设计出被称为“交互相移掩膜(Alternating Phase Shift Masks)”的新颖技术,这项技术可用现有的193nm波长制作35nm的线宽,从而能够让193nm波长的光刻设备继续用于65nm工艺的芯片制造中,而该设备目前广泛用于90nm精度的芯片生产中。英特尔的目标是让现在的248nm波长的光刻设备也能够得到再利用,该设备现在用于130nm工艺的芯片制造。如果不用大规模更换设备,65nm工艺的实施成本便能够显著降低,芯片的量产工作也得以快速实现,这对英特尔的发展可谓至关重要的一环。

在此之后,英特尔将导入超紫外光微影技术(EUV Lithography),可以提供13nm波长,大幅超前现有的微影技术,英特尔也是目前唯一全力投入该技术研发的半导体厂商。

三、结语

65nm技术的到来是否让你产生许多的联想?据悉:Intel其65nm技术已经进入了最后测试阶段,包括了Mobile、Desktop及Server级的处理器,而到了2005年第4季度,65nm的Yonah双内核样本将会推出。同时除了俄勒冈州的D1D工厂外,英特尔还投入20亿美元巨资改造位于爱尔兰的Fab 24-2芯片制造厂。该工厂准备于2006年前投入65nm芯片的大批量生产,而俄勒冈州的D1D工厂则会首先进入先期投产阶段,之后其他的十几座芯片工厂也都将逐渐进行新工艺的转换。可以说,作为半导体制造技术的先行者,英特尔在65nm大潮中再次领先……