从Prescott谈CPU背后的生产技术

硬件周刊

2月1号,英特尔发布了新一代处理器──Prescott。它的问世预示着英特尔将全面转向0.09μm(微米)制程时代。除了关注新处理器的性能变化外,与CPU生产相关的技术也再次成为大家所关注的焦点。

一、蚀刻尺寸与制程

许多对电脑知识略知一二的朋友大多会知道,CPU里面整合了成千上万个晶体管,如果要提高CPU的功能,最重要的一点就是如何在相同的CPU面积里面放进去更多的晶体管。简单地以集成元件数量为例,单芯片上的晶体管集成数量已经在1965年的302个的基础上取得了惊人的增长成绩:1975年,这个数值已经达到了65000个,2002年采用0.13μm制程的P4中已经集成了5500万个晶体管,而目前最新处理器的晶体管数量已经突破了1亿个大关。但随着集成度的提高,电路复杂性也随之提高。那么厂商是如何在处理器那么狭小的空间内集成越来越多的晶体管呢?关键是必须进一步缩小硅晶片内的微细元件的尺寸,以腾出空间容纳增加的晶体管和元件。深入了解就涉及到一个技术参数──蚀刻尺寸。

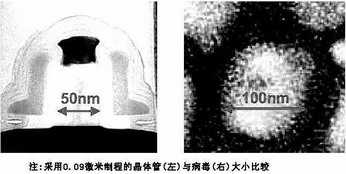

蚀刻尺寸是制造设备在一片硅晶元上所能蚀刻的一个最小尺寸。蚀刻也称为光刻,该技术利用一定波长的紫外线透过掩膜后照射在硅晶元上,将掩膜上的电路图像完整地复制到硅晶元上从而形成所需要的电路图形的(提示:掩膜其实可以看作是CPU内核电路图的微缩“底片”,厂商事前先将一幅非常复杂的设计模型原图缩小成极细微的蚀刻掩膜)。蚀刻中最关键的地方就是紫外线的波长,波长越短的紫外线干扰和衍射现象就越不明显,晶体管就可以实现越小的线宽。目前在CPU制造中主要是采用2489埃波长的氪/氟紫外线(1埃=0.1nm),主要应用于0.18μm和0.13μm制程中。目前英特尔最新的0.09μm制程则采用了波长更短的1930埃的氩/氟紫外线。因此当你听见Pentium 4采用0.13μm制程时,这意味着Pentium 4的晶体管尺寸最小可以做成0.13μm那么大,就是说这个加工厂在晶元上所能蚀刻的最小晶体管尺寸是0.13μm。通常,“蚀刻尺寸”和“晶体管尺寸”这两个术语是可以交换使用的。

蚀刻尺寸越小,那么单个晶体管通道(也称晶体管间的物理门长)就越小,从而可以腾出更多的空间来容纳更多的晶体管。采用0.13μm的Pentium 4的单个晶体管通道为60nm(纳米),而采用0.09μm的Prescott的单个晶体管通道已经降到了50nm。而且蚀刻出来的线条越细,也可以增加内核心中铜线路互联的层数。

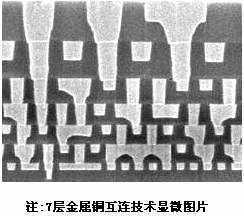

目前CPU中集成的晶体管数目已经数以亿计,厂商为了能在有限的CPU内核空间集成更多的晶体管往往使用一种三维的堆叠结构。在0.13μm制程时代已经有厂商使用了7层布线结构。Intel在这场竞赛中已经是个落后者,到了0.09μm时代,Intel才刚刚采用7层布线结构,同一时间IBM已经宣布将会全面转入8层布线结构。CPU集成的晶体管按照摩尔定律不断增加,因此用于连接各部分的金属电路的重要性也开始凸现,在CPU中金属电路的传导能力甚至决定了CPU所能提供的最高速度。在0.09μm制程中,Intel 将使用碳硅混合物取代目前的SiOF,从而提高了18%的互连效率。而且利用0.09μm技术,Intel已经可以将一个6个晶体管的SRAM单元做在了1μm2的面积中。这样一个52Mbit的10mm×11mm芯片就可以包含3.3亿个晶体管,是Pentium 4处理器的7倍。而且用更先进的生产工艺可以降低晶体管的功耗,增加处理器的频率提升潜力。不过,一套特定的生产设备的蚀刻尺寸是固定的,所有的硅晶圆制造厂都是按某几个特定的蚀刻尺寸来生产芯片。

值得一提的是,目前更先进的EUV(Extreme Ultraviolet,极端远紫外光)蚀刻技术已经出现。EUV与传统的紫外线蚀刻技术原理是一样的,都是将激光通过掩膜,把掩膜上的电路图转移到晶圆之上,不过EUV设备使用的是13.4nm波长的激光,采用部分波长极短的电磁频谱,因此能实现更小的蚀刻尺寸。Intel希望在2005年开始使用EUV技术,那个时候他们也将用0.045μm制程生产芯片了。

二、先进制程的背后

四然采用更先进的制程,厂商可以在CPU内整合更多的晶体管,但问题也相应而至。其中泄漏电流就成为CPU厂商需要解决的问题之一。

现阶段CPU制造过程中晶体管本身存在的漏电问题。目前存在着两种泄漏电流:首先是门泄漏,这是电子的一种自发运动,由负极的硅底板通过管道流向正极的门;其次是通过晶体管通道的硅底板电子自发从负极流向正极的运动,这也被称为亚阈泄漏。这两种泄漏电流都需要提高门电压以及驱动电流来进行补偿,这对CPU的能量消耗以及发热量都有负面的影响,存在泄漏电流问题也是AMD迟迟不能启用0.09μm制造工艺的原因之一。

此前,CPU厂商一般在门和通道之间增加一个绝缘SiO2层充当电子屏障,来防止门泄漏。但为了减小单个晶体管通道宽度、腾出更多的空间,目前厂商已经将这个薄层的厚度逐渐减小到整个通道长度的1/45。不过薄层屏蔽效果是有限度的,当绝缘SiO2薄层的厚度小于2.3nm,门泄漏所带来的负面影响将变得相当严重。那么如何既减小单个晶体管通道的宽度又能降低门泄漏的影响呢?

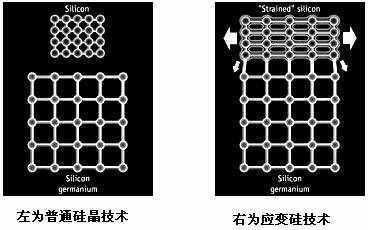

针对这个问题,英特尔在Prescott中引入了一种称为“应变硅(Strained silicon)” 技术来解决。应变硅属于一种超薄的氧化物。该层氧化物达到了1.2nm厚度的极限,它仅有通道的1/45。不过应变硅的作用和目前使用的SiO2刚好相反,SiO2是作为电子的屏蔽层出现的,在其下的通道则是电子由发射端到接收端的路径,电流越高,电子运动就越容易,速度也越快。通道一般是用硅制成的,如果使用应变硅代替普通的硅来制造晶体管通道的话,格子里的原子将被分散在较远的距离、可以将原子拉长,那么电子在通过稀疏的原子格时遇到的阻抗就大大下降。Intel宣称利用这种技术只须将Si原子拉长1%,就可以提高10%~20%的电流速度,而成本只增加了2%。而AMD正准备在其64位处理器中使用SiGe技术(其实属于SOI技术)来取代纯粹的硅来作为驱动电流的通道,功效和Intel的应变硅技术有些类似。使用此种技术就可以使粘结硅层做得更薄更均匀。AMD的技术似乎更具有优势:通过此技术,晶体管的硅晶格会根据下面的元素的晶格调整自己,并将延展一些,潜在的阻抗将会比普通的硅下降70%,而晶体管性能将提高35%。

至于亚阈泄漏的问题,在目前所有的解决方案中,SOI(Silicon on Insulator,绝缘层上覆硅)看上去是最有前景的方案。其原理很简单:晶体管通过一个更厚的绝缘层从硅晶元中分离出来,这样做具有很多优点。首先,利用SOI技术,晶体管“开”和“关”状态的切换性能提高了,而且同时在速度不变的情况下,我们也可以降低阈值电压或是同时提高性能和降低电压。举个例子来说,如果阈值电压保持不变,性能可以提高30%,如果我们将频率保持不变而将目的集中在节能性上,那么我们也可以节省大约50%的能量。

此外,当晶体管本身可以处理各种错误时,通道的特性也变得容易预计了。但SOI技术也有不足之处,它必须减小晶体管漏极/源区域的深度,这将导致晶体管阻抗的升高,而且晶体管的成本也提高了10%。为此英特尔别树一帜,引入了一种称DST(depleted substrate transistor)的技术。Intel一直对SOI技术抱着怀疑的态度,认为使用完全耗尽的通道没有任何好处,过小的晶体管通道宽度会大大增加制造难度,同时也因为发射端和接收端的距离减小会急剧提高外接晶体管的阻抗。这个DST技术通过一些改动来消除SOI技术的主要缺点,这样即使通道真的非常短,利用DST技术做了贫化处理,完全让电阻在控制之下。驱动电流可以立即在门下通过,并不会电离在绝缘层下通道的任何部分。不过DST技术也带来一个问题,那就会增加外接晶体管的阻抗,所以,Intel为了不让通道的长度影响到DST晶体管上的漏极和接收端的长度。Intel通过降低“关”状态电压有效地将产品工作电压降到了1.0V以下,并表示可以在2010年达到0.6V。

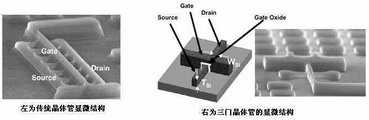

此外,随着晶体管的尺寸不断缩小以及硅晶片上排列更紧密并以极高速度运转,能量消耗以及热量的产生将成为处理器频率继续提升的最大障碍。为了应付这种晶体管高密度所带来的能量密集的问题。英特尔开发了一种称为三门晶体管技术,以期在提高性能的同时也能提高能源的利用率。

三门晶体管就是在单个晶体管内集成三个通道。从微观上看,三门晶体管的门(gate)、发射器(emitter)和收集器被设置在普通晶圆的表面,并且它们之间相互交叉。这样就构成了一种有趣的结构:门电子束的截面是一个矩形,顶端和两侧都是门电极,这样一来,三门晶体管就像是反转的传统晶体管竖立在了晶圆上。(注:传统的晶体管架构呈现为二维的状态,包括1个可以控制的电极和在它下面的电流顺序通过的另外两个电极)

普通晶体管只在顶端有一个门电极,也就需要更多的时间在通道上切换充电状态以改变晶体管的开关状态,同时也需要更高的电压。而通过三门晶体管技术,理论上只需要有几束相同的电波我们就够通过使用极限的电压打开晶体管,几乎同时门会被出现在所有电波上的电流而阻断。所以通过晶体管的总电流等于每个交叉点的电流之和。假设我们有6个输出,其中三个发射器,三个接收器,那我们可以得到与普通晶体管相同的电流,但相同情况下所需要输入的电压却仅为1/3。或者相同的电压可以驱动3倍于以前的电流,总体效率将提高20%。而且三门晶体管的高效性降低了对通道长度的要求,可以大大降低对生产技术的要求。不过这项技术目前还停留在实验室阶段,还没有在Prescott上应用。当然AMD也在考虑多门晶体管,不过AMD所推的是双门晶体管技术,和Intel的三门晶体管不同,它没有上方的控制电极。双门晶体管的宽度大约为门极宽度的1/3,晶体管发送/接收的电子束也要窄一些,但由于单个晶体管通道宽度大大减小,这对蚀刻技术提出了更高要求。不过双门晶体管相对于传统的晶体管都有很多的优势,特别是它缩小了通道长度。

小结:

在过去的40多年,半导体工业的发展解决了一个又一个看似不可能突破的瓶颈,神奇地遵循着摩尔定律向前发展着。而这一切都得益于生产技术的不断进步,可以预见这种发展趋势仍将持续下去……