QBM内存──未来的DDR内存

硬件周刊

虽然我们知道现在已经开发出了高达6GB/s的DDRII SDRAM,还有5.4GB/s的DDR333,但这两项产品真正上市也只能等到2003年之后。而QBM却可以使用现有的DDR266和DDR333内存在一个时钟周期内传输次4次数据,并稳定工作在高出原来1倍的宽带之上。由于QBM只需使用传统的DDR模块,而且接口也与现在的DDR一样,厂家无须进行设备改进,即可生产出相对于以前两倍宽带的DDR内存。因而QBM内存规范才成为众多厂家追求的目标。

QBM内存的结构

采用QBM技术的内存模组由两个DDR模块构成,其一按照正常的速度工作,另一则延迟1/4周期,每一模块连接一个场效应管。场效应管在此起开关缓冲的作用。在它的作用下,时钟周期被错开的模块在一个10ns的周期内共同提供4bits的数据吞吐量。而普通的DDR内存在同样一个周期内能实现的吞吐量是2bits,标准的SDRAM只能实现1bits。Rambus在此之前已经展示了同样能在一个周期达到4bits吞吐量的Quad Ram bus技术,但在原理上和QBM是大相径庭的。Rambus应用了芯片接口技术来分离工作电压,4bits数据分别通过4种电压不同的电平信号在同一个周期内传输;而QBM技术依靠的是外部缓冲开关机制来实现在1/4个周期内传输1bits的数据。从表面上看,Kentron的方案比Rambus实现方法要简单得多。这意味着具有成本低廉的优势((图1)为QBM内存的成品图)。

QBM内存的特点

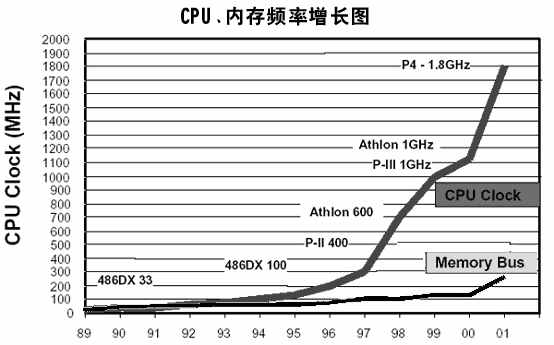

由(图2)可以看到,从1989年开始一直到2001年,在这么长的时间里,CPU的工作频率差距和内存的工作频率差距是越来越大。我们可以拿Intel P4处理器来举个实际例子。虽然最高FSB频率可以达到400MHz,但是如果使用DDR2100内存,其内寸带宽最多也就2.1GB/s。这样依然无法满足P4的内存带宽要求,因为P4处理器平台理想的带宽是3.2GB/s。虽然目前支持P4平台的主板芯片组很多,包括可以使用SDRAM和DDR的Intel i845、i845D和VIA的P4X266。但最能发挥P4性能的内存还得算i850和Rambus。即使采用了未来即将推出的DDR333内存,也无法满足P4处理器对内存带宽的要求。因为DDR333内存最高也只能提供2.7GB/s的带宽。P4处理器所需带宽则是3.2GB/s,这样二者之间还是差了500MB/s。虽然我们知道与P4搭配最完美的还是双管道Rambus内存,但是Rambus的成本一直居高不下,而且使用Rmabus的主板也比普通主板较贵,所以Rambus也不是最理想的内存。按这种速度发展下去,内存瓶颈问题依然得不到解决。在2002年里Intel会再一次提升处理器的前端总线,推出FSB为533MHz的North Wood核心的P4,如果还继续使用现有的内存,这个差距可就真的难以弥补了。但Kentron很快站出来公开发表声明,在2002年也会同时发布133MHz的QBM内存,而它的内存带宽已经达到了4.2GB/s。

QBM内存工作方式

其实QBM内存与DDR内存是没有多大区别的,在针脚和芯片定义上都一样,也是184pin,但是在QBM内存条每两个模块下方会多一个FET芯片。QBM和DDR为了提高传输带宽,都是采取减少数据传输时钟周期的办法。DDR是在时钟频率的上下沿都传输数据来达到提高带宽。QBM则作了改进,一个QBM模组由两个DDR模块组成,其中一个模块运行在正常频率的速度,而另外一个的模块的时钟周期比前一个模块时钟周期正好慢90°的相位差,也就是说两者的工作起始时间相差1/4个时钟周期,通过这种简单的方法来让QBM得到两倍于DDR内存的工作效率,即一个时钟周期实现了4次数据读写。

QBM内存模组中的两个DDR模块由一个FET芯片连接,这个FET芯片的作用是延迟开关,它起到了场效应管(一种电压控制器件)和串联的作用。场效应管除了可以实现更高速度的数据传输,还可以减轻系统的电容负载。电容负载问题在很大程度上束缚了总线速度和存储密度的提升。

QBM内存的未来

Kentron会在今年的第一季度推出400MHz工作频率的QBM400和533MHz工作频率的QBM533。2003年推出QBM667,2004年推出QBM800,而DDR这时最快也才是DDR400,可见QBM的发展速度之快。还值得庆幸的是,在VIA最新发布的P4X333芯片组中,除了支持PC2700 DDR、AGP 8X以及V-Link/533外,还加了对QBM内存技术的支持。不过QBM还必须经受DDRⅡ或者DDR+规范的冲击。后两种内存似乎价格更高,因此未来可能还是属于QBM的。毕竟QBM的成本低、生产容易而且已经有正式的样品了。希望QBM内存能尽快走入我们的生活。